# 17<sup>th</sup> EMBEDDED SYSTEMS WEEK

OCTOBER 08-15, 2021 | VIRTUAL CONFERENCE

## 2021 ESWEEK PROGRAM

### SPONSORING SOCIETIES:

## Thank You to Our Sponsoring Societies

## Thank You to Our Platinum Sponsors

## Thank You to Our Gold Sponsors

# TABLE OF CONTENTS

---

|                                              |              |

|----------------------------------------------|--------------|

| <b>Sponsors.....</b>                         | <b>2</b>     |

| <b>General Chairs' Welcome Message.....</b>  | <b>4-5</b>   |

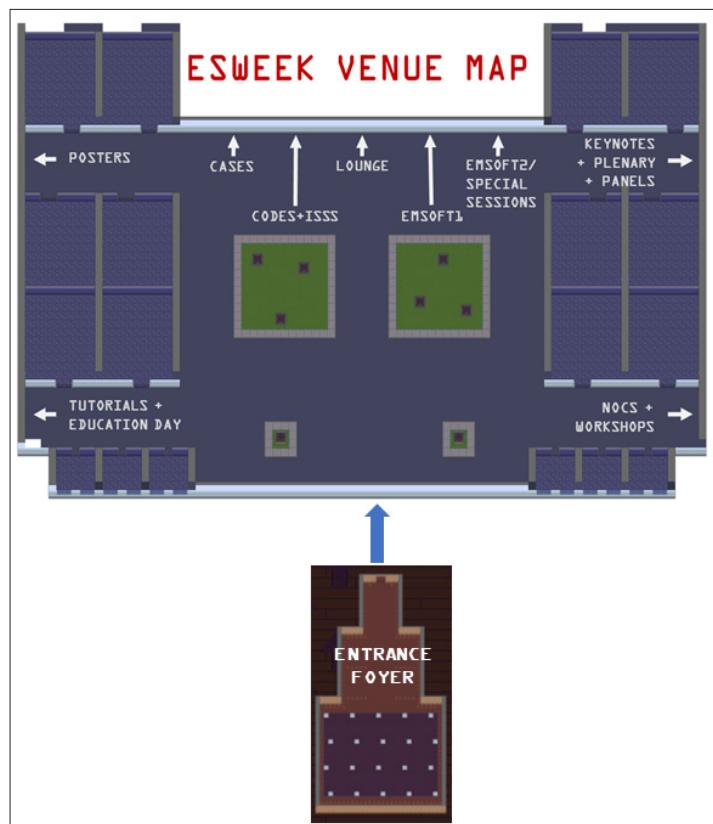

| <b>ESWEEK Virtual Conference Layout.....</b> | <b>6</b>     |

| <b>ESWEEK 2021 Overview .....</b>            | <b>7</b>     |

| <b>Best Paper Candidates .....</b>           | <b>8</b>     |

| <b>Tutorial Schedule .....</b>               | <b>9-15</b>  |

| <b>Education Schedule .....</b>              | <b>16-25</b> |

| <b>Monday Program .....</b>                  | <b>26-36</b> |

| <b>Tuesday Program .....</b>                 | <b>37-47</b> |

| <b>Wednesday Program .....</b>               | <b>48-57</b> |

| <b>Workshops .....</b>                       | <b>58-59</b> |

| <b>Symposium .....</b>                       | <b>60-64</b> |

| <b>ESWEEK 2021 Committee .....</b>           | <b>65</b>    |

| <b>CASES 2021 Committee .....</b>            | <b>66-67</b> |

| <b>CODES + ISSS 2021 Committee.....</b>      | <b>68-69</b> |

| <b>EMSOFT 2021 Committee .....</b>           | <b>70-71</b> |

| <b>NOCS Committee.....</b>                   | <b>72-73</b> |

Andreas Gerstlauer, General Chair

*The University of Texas at Austin, USA*

Aviral Shrivastava, Vice-General Chair

*Arizona State University, USA*

## Welcome to the Virtual edition of ESWEEK 2021!

Embedded Systems Week (ESWEEK) is the premier event covering all aspects of hardware and software design for smart, intelligent and connected computing systems. By bringing together three leading conferences (CASES, CODES+ISSS, EMSOFT), a symposium (NOCS) and several workshops and tutorials, ESWEEK allows attendees to benefit from a wide range of topics covering the state of the art in embedded systems research and development.

Due to the on-going pandemic, this 17th edition of ESWEEK will remain fully virtual this year. However, ESWEEK 2021 still promises to be a very exciting and engaging event. It consists of tutorials, keynotes, paper sessions with live talks and interactive poster presentations every day that, together with a very low registration fee, provide an opportunity for the community across the globe to come together, engage, interact, and celebrate the latest advances in embedded software and systems. New this year is an Education Track in which top international researchers present short courses on various new/emerging but well established fundamental embedded system topics with “embedded learning” as the theme this year. In addition, we have for the first time established a registration fee waiver program that will allow attendees with demonstrated need, e.g. students and researchers from developing countries with limited financial funds or means (e.g. access to credit cards) to attend ESWEEK for free.

Following the journal-integrated publication model for the three conferences (CASES, CODES+ISSS, and EMSOFT),

all regular papers presented are published in a Special Issue of the ACM Transactions on Embedded Computer Systems (TECS). To this end, ESWEEK-related journal submissions to TECS followed a journal-style peer review process conducted in two stages with the opportunity of minor/major revisions before the final decision. In addition, the selected Work-in-Progress (WiP) track papers are published in conference-specific Proceedings.

The technical program on Monday, Tuesday, and Wednesday consists of 4 special sessions and 17 regular sessions from the three conferences. There is a strong emphasis on interaction in the virtual setting. All the accepted journal-track and WiP papers along with prerecorded lightning video presentation for each paper are made available to the ESWEEK participants two weeks before the virtual event. During the conference week, the live technical sessions will feature 15 minute talks for the journal-track papers including Q&A. In addition, all journal-track and WiP papers will be accompanied by interactive virtual poster sessions in which attendees can further interact with presenters and authors.

Tuesday will be a special Industry Day at ESWEEK. The day will be framed by two special industry sessions on on collaborative industry-academia European research projects before the main conference, and an industry pitch session concluding the day in which speakers from industry will outline design challenges aimed at fostering discussion between experts, increase awareness about practical challenges, and allowing academic researchers to put their research into the context of industrial needs.

Wednesday will be a special Edge AI Day focusing on

research related to machine learning (ML) and artificial intelligence (AI) on embedded, edge and IoT devices. In addition to relevant journal-track paper sessions, the Wednesday keynote, two special sessions and a final panel concluding the day are devoted to this subject.

Highlights of the ESWEEK program are three distinguished keynote talks by prominent leaders in academia and industry, covering relevant trends for future embedded and cyber physical systems and providing deep insights into technology drivers. Mike Davies from Intel will introduce the latest advances in neuromorphic computing for fast, efficient, and intelligent processing on Monday. On Tuesday, Professor Claire Tomlin from UC Berkeley will talk about safe learning in robotics. Finally, as part of the Edge AI Day on Wednesday, Pete Warden from Google will discuss the needs, challenges and opportunities associated with machine learning on embedded systems.

The main conference program will conclude with a panel on Wednesday as part of the Special Edge AI Day focusing on “Machine Learning on the Edge: How Deep Can We ‘Embed’ It Into the Cloud-Edge Continuum?”. Top experts will share their views on this highly relevant topic.

The main program is preceded by tutorials on the Friday before the conference week, and Education Classes on Saturday and Sunday. These provide an excellent opportunity to get in-depth knowledge on both new trends and hot topics as well as emerging but well-established embedded systems concepts, tools and methods that are not readily available in textbooks. There are six half-day, virtually presented academic and industry tutorials, covering a wide scope from quantum computing, fog computing for IoT and deterministic programming of CPS to edge AI, compute acceleration and GPU code generation products from Intel, Xilinx and MathWorks. The theme for ESWEEK Education Classes this year is “Embedded Learning”. Twelve classes will provide an exciting, engaging and hands-on way to learn about

**We are looking

forward to seeing you

virtually at the

inspiring, interesting,

and interactive

ESWEEK 2021!**

topics ranging from neuromorphic computing to edge ML and autonomous driving to students across the globe, especially the ones that do not have access to high quality educational content.

Thursday and Friday of the conference week are the days for the symposium and workshops. Besides the NOCS (Networks on Chip) symposium, we have three workshops covering a range of important topics in embedded systems: RSP (Rapid System Prototyping), TRAIN (Trustworthy and Reliable Accelerator Design), and MSC (Memory and Storage Computing).

The organization of ESWEEK was only possible with the continuous support and help from the sponsors and many volunteers: The program chairs with their program committee members, the organizers of the workshops, tutorials, and symposia, all members of the organization committee, and, last but not least, the virtual conference chair and the web chair--without their commitment and contributions this virtual event would not exist.

We are looking forward to seeing you virtually at the inspiring, interesting, and interactive ESWEEK 2021!

Sudeep Pasricha,

Virtual Conference

Chair

*Colorado State

University, USA*

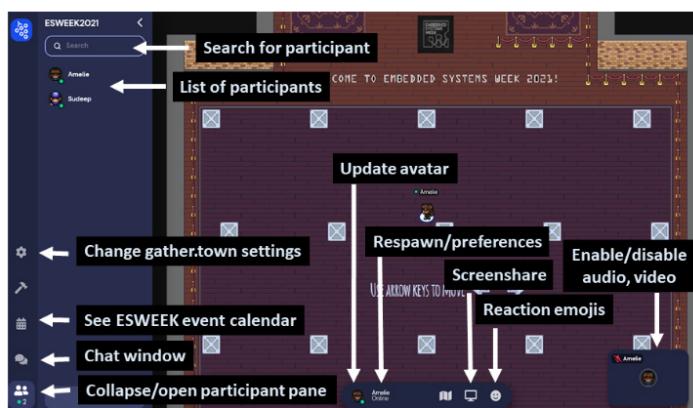

ESWEEK 2021 has a dedicated virtual space, hosted on the Gather.town platform, for conference attendees to interact with other attendees and presenters during the week. In this virtual space, you can attend interactive poster sessions, post-presentation Q&A sessions, and view livestreams of talks for all CASES/CODES+ISSS/EMSOFT technical sessions, keynote and plenary sessions, and co-located symposia (NOCS) and workshops (RSP/TRAIN/MSC). You can visit industry sponsor booths to engage with their representatives. The virtual platform allows you to search for a specific ESWEEK attendee and chat with them via text or video. You can also have a video chat with a person who is close enough with you or with people in the same private space as you.

You will sign into the ESWEEK 2021 virtual space using the link and passcode received from the organizers (a few days before the conference begins). After signing in, the user interface (UI) will have options to edit your avatar, enable/disable your mic and video, see/find other attendees, interact with people and objects, and to quickly teleport to (or get directions to) any scheduled session. The UI image shows annotations to highlight the key UI elements.

The Gather.town space for ESWEEK 2021 consists of 9 areas, as shown in the venue map. Four rooms are dedicated to the four parallel sessions; one each for CASES and CODES+ISSS, and two for EMSOFT and special sessions. Another room is dedicated for plenary sessions, keynotes, and panels. A lounge area provides a dedicated social space. The posters area leads to separate rooms for WIP posters and dedicated interactive spaces for Q&A with authors of all accepted papers after their talks. The tutorials and education day area leads to dedicated rooms for all tutorials and education day sessions. The NOCS and workshop area leads to rooms dedicated to the RSP/TRAIN/MSC workshops and the NOCS symposium. All rooms are connected together and can be reached from anywhere in the map, just like at a real conference venue. You can also use the ESWEEK event calendar in your UI to teleport to any ongoing or upcoming sessions.

# ESWEEK 2021 OVERVIEW

| Friday, October 8                                                                                                             | Saturday, October 9                                                                                                                                         | Sunday October 10                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials                                                                                                                     | Education Classes                                                                                                                                           | Education Classes                                                                                                                                                                                         |

| Monday, October 11                                                                                                            | Tuesday, October 12                                                                                                                                         | Wednesday, October 13                                                                                                                                                                                     |

| ESWEEK Opening<br>Keynote by Mike Davies<br>CASES, CODES+ISSS, EMSOFT and Special Sessions<br>Work-in-Progress Poster Session | Test of Time Awards<br>Keynote by Claire Tomlin<br>Industry Sessions<br>CASES, CODES+ISSS, EMSOFT and Special Sessions<br>Industry Pitch and Poster Session | Best Paper and Other Awards<br>Keynote by Pete Warden<br>CASES, CODES+ISSS, EMSOFT and Special Sessions<br>Panel: Machine Learning on the Edge: How Deep Can We 'Embed' It Into the Cloud-Edge Continuum? |

| Thursday, October 14                                                                                                          | Friday, October 15                                                                                                                                          |                                                                                                                                                                                                           |

| NOCS Opening<br>NOCS Keynote by Keren Bergman<br>NOCS Sessions<br>MSC Workshop<br>TRAIN Workshop<br>RSP Workhop               | NOCS Keynote by Gabriel (Gabe) Loh<br>NOCS Sessions                                                                                                         |                                                                                                                                                                                                           |

## CASES

### 1A.1 RiSA: A Reinforced Systolic Array for Depthwise Convolutions and Embedded Tensor Reshaping

Authors:

Hyungmin Cho - Sungkyunkwan University

### 3A.3 Two Birds with One Stone: Boosting Both Read and Write Performance for Tree Indices on Persistent Memory

Authors:

Yongping Luo, Peiquan Jin, Zhou Zhang, Juncheng Zhang - University of Science and Technology of China

Qinglin Zhang, Bin Cheng - Tencent

### 3A.4 You Only Traverse Twice: A YOTT Placement, Routing, and Timing Approach for CGRAs

Authors:

Michael Canesche - Universidade Federal de Viçosa (UFV)

Westerley Carvalho - Universidade Federal de Viçosa (UFV)

Lucas Reis - Universidade Federal de Viçosa (UFV)

Matheus Oliveira - Universidade Federal de Viçosa (UFV)

Salles Magalhães - Universidade Federal de Viçosa (UFV)

Peter Jamieson - Miami University

José Augusto Nacif - Universidade Federal de Viçosa (UFV)

Ricardo Ferreira - Universidade Federal de Viçosa (UFV)

## CODES+ISSS

### 1B.2 Exploring Efficient Architectures for Remote In-Memory NVM over RDMA

Authors:

Qingfeng Zhuge, Hao Zhang, Edwin Hsing-Mean Sha, Rui Xu - East China Normal University

Jun Liu, Shengyu Zhang - Lenovo Ltd.

### 2B.2 Intermittent-Aware Neural Architecture Search

Authors:

Hashan Mendis, Chih-Kai Kang, Pi-Cheng Hsiao - Academia Sinica

### 4B.1 MARS: mmWave based Assistive Rehabilitation System for Smart Healthcare

Authors:

Sizhe An and Umit Ogras - University of Wisconsin-Madison

## EMSOFT

### 1C.4 Excluding Parallel Execution to Improve Global Fixed Priority Response Time Analysis

Authors:

Quan Zhou, Jianjun Li, Guohui Li - Huazhong University of Science and Technology

### 2D.1 Towards an Integrated Vehicle Management System in DriveOS

Authors:

Soham Sinha and Richard West - Boston University

### 3C.1 Verified Lustre Normalization with Node Subsampling

Authors:

Timothy Bourke, Basile Pesin, Paul Jeanmaire - Inria / ENS

Marc Pouzet - Ecole normale supérieure

## NOCS

### I.1 A Novel Network Fabric for Efficient Spatio-Temporal Reduction in Flexible DNN Accelerators

Authors:

Francisco Muñoz-Martínez - Universidad de Murcia

Jose L. Abellán - Universidad Católica San Antonio de Murcia

Manuel E. Acacio - Universidad de Murcia

Tushar Krishna - Georgia Institute of Technology

### III.1 PlugSMART: A Pluggable Open-Source Module to Implement Multihop Bypass in Networks-on-Chip

Authors:

Alireza Monemi - Barcelona Supercomputing Center

Iván Pérez - University of Cantabria

Neiel Israel Leyva - Barcelona Supercomputing Center

Enrique Vallejo - University of Cantabria

Ramón Beivide - University of Cantabria

Miquel Moreto - Barcelona Supercomputing Center

# TUTORIALS SCHEDULE

Friday, October 08

## TUTORIALS

9 am - 1 pm, EDT

### T1. QuantumFlow: A Co-Design Framework of Neural Network and Quantum Circuit towards Quantum Advantage

Weiwen Jiang, *George Mason University, USA*

Jinjun Xiong, *IBM T.J. Watson Research Centre, USA*

Yiyu Shi, *University of Notre Dame, USA*

9 am - 2 pm, EDT

### T2. Fog Computing for Industrial IoT

Alessandro V. Papadopoulos, *Mälardalen University, Sweden*

Wilfried Steiner, *TTTech Computertechnik AG, Austria*

9 am - 1 pm, EDT

### T3. Deterministic Reactive Programming for Cyber-Physical Systems Using Lingua Franca

Soroush Bateni, *University of Texas at Dallas, USA*

Hokeun Kim, *Hanyang University, South Korea & UC Berkeley, USA*

Edward A. Lee, *UC Berkeley, USA*

Shaokai Lin, *UC Berkeley, USA*

Marten Lohstroh, *UC Berkeley, USA*

Christian Menard, *TU Dresden, Germany*

Efsane Soyer, *UC Berkeley, USA*

## INDUSTRIAL TUTORIALS

9 am - 1 pm, EDT

### IT1. Scalable SoC Architecture for Edge AI Products

Pawan Chhabra, *Intel*

Ajay Upadhyaya, *Intel*

### IT2. Integrating Compute Acceleration Into Embedded System Design Using Vitis

Parimal Patel, *Xilinx*

### IT3. GPU Code Generation from MATLAB

Jack Ferrari, *Mathworks Inc.*

**Tutorial T1, 9 am - 1 pm, EDT**

## QuantumFlow: A Co-Design Framework of Neural Network and Quantum Circuit towards Quantum Advantage

This tutorial presents a recently proposed co-design framework for neural networks and quantum circuits. It comprises (1) a lecture session on quantum machine learning, including the fundamentals of quantum computing, an overview of quantum machine learning, and the mapping of neural networks onto quantum circuits; (2) a hands-on session using IBM Qiskit to program neuron computation with quantum circuits; (3) a lecture and hands-on hybrid session of co-design neural network and quantum circuit to optimize the quantum implementation with the consideration of noise in qubits. The tutorial targets experts and students in artificial intelligence, machine learning, quantum computing, compiler and architecture optimization, and hardware/software co-design and system synthesis.

Along with the rapid development of quantum computers, e.g., Google's Sycamore with 53 qubits and IBM's Hummingbird with 65 qubits, there is a growing interest in pursuing quantum supremacy or advantages over classical computers in various applications. Machine learning is one of the most promising applications because (1) it encounters the computation-/memory-bound on classical computing and (2) the linear algebra at its core is also central to quantum computing.

### Organizers and speakers:

Weiwen Jiang, *George Mason University, USA*

Jinjun Xiong, *IBM T.J. Watson Research Centre, USA*

Yiyu Shi, *University of Notre Dame, USA*

### Bio:

**Weiwen Jiang** will join George Mason University as a Tenure-Track Assistant Professor. He is a Postdoctoral Associate at the University of Notre Dame. He received his Ph.D. degree from Chongqing University in 2019. From 2017 to 2019, he was a research scholar at the University of Pittsburgh. His research interest is on hardware and software co-design; in particular, the co-design of neural networks and different hardware accelerators, including mobile devices, FPGA, and ASIC. Most recently, he moves to the co-design of neural networks and quantum circuits.

His work demonstrates the quantum advantages for neural networks for the first time, which has been published at *Nature Communications*. Dr. Jiang's research works have been published in prestigious journals and conferences, including *Nature Electronics*, *Nature Communications*, *IEEE/ACM Transactions*, *DAC*, *ICCAD*, *ESWEEK*, *GLSVLSI*, etc. He is the receipt of Best Paper Award in *ICCD'17* and Best Paper Nominations in *DAC'19*, *CODES+ISSS'19*, *ASP-DAC'16*, and *ASP-DAC'20*.

**Jinjun Xiong** is currently the Program Director for Cognitive Computing Systems Research at the IBM Thomas J. Watson Research Center. He is responsible for defining the scientific agenda and strategic directions for advanced cognitive computing systems research across industries, academia and governmental agencies. In that capacity, he co-directs the IBM-Illinois Center for Cognitive Computing Systems Research (C3SR). Prior to that role, Dr. Xiong was a manager of the Smarter Energy group, responsible for the IBM Research's Big Bet Program on Smarter Energy Research, including its strategies and execution. Dr. Xiong received his Ph.D. degree in Electrical Engineering from University of California, Los Angeles in 2006, and since then has been a Research Staff Member with IBM Thomas J. Watson Research Center. His research interests include quantum computing, cognitive computing, big data analytics, deep learning, smarter energy and application of cognitive computing for industrial solutions.

**Yiyu Shi** is currently an associate professor in the Department of Computer Science and Engineering at the University of Notre Dame, the site director of NSF I/UCRC Alternative and Sustainable Intelligent Computing, and a visiting scientist at Boston Children's Hospital, the primary pediatric program of Harvard Medical School. His current research interests focus on hardware intelligence with biomedical applications. He has published over 200 peer reviewed papers in premier venues such as *Nature* research journals, including more than a dozen best papers or nominations in top conferences. He was also the recipient of IBM Invention Achievement Award, Japan Society for the Promotion of Science (JSPS) Faculty Invitation Fellowship, Humboldt Research Fellowship, IEEE St. Louis Section Outstanding Educator Award, Academy of Science (St. Louis) Innovation Award, Missouri S&T Faculty Excellence Award, NSF CAREER Award, the Air Force Summer Faculty Fellowship, IEEE Computer Society Mid-Career Research Achievement Award, and Facebook Research Award. ■

**Tutorial T2, 9 am - 2 pm, EDT**

## Fog Computing for Industrial IoT

The tutorial presents novel architectures, hardware and software platforms, applications, and data-driven techniques for enabling fault tolerance in Industrial IoT and Fog Computing systems. It comprises theoretical and hands-on components with a focus on fault tolerance. Researchers and practitioners will hear about the challenges and opportunities of recent developments and trends. Industrial IoT refers to IoT systems used in the industrial areas to interconnect machines. It provides the infrastructure that underpins Smart Energy Grids, Smart Cities, Smart and Green Mobility, Smart Manufacturing, etc., and provides solutions for several societal challenges. Fog Computing is a system-level architecture that distributes resources and services from computing, storage, control and networking anywhere along the continuum from Cloud to Things. It is one of the key elements of the IIoT and Industry 4.0. Fog Computing will be enabled by the increased usage of IP-protocols, e.g., standardized Deterministic Ethernet solutions from IEEE Time-Sensitive Networking (TSN)4 Task Group, upcoming 5G wireless standards, and interoperability standards such as OPC Unified Architecture (OPC UA). The resulting integrated Fog Computing platform brings computation, communication and storage closer to the edge of the network.

### Organizer(s):

Alessandro V. Papadopoulos, *Mälardalen University, Sweden*

Wilfried Steiner, *TTTech Computertechnik AG, Austria*

### Speakers:

Wilfried Steiner, *TTTech Computertechnik AG, Austria*

Karl-Erik Årzén, *Lund University, Sweden*

Ivona Brandic, *TU Wien, Austria*

Atakan Aral, *TU Wien, Austria*

### Bio

**Alessandro V. Papadopoulos** is an Associate Professor of Computer Science Systems and Control at Mälardalen University (MDH), Sweden. From 2020, he is scientific advisor of ABB Industrial Automation, Sweden. He received his Ph.D. degree in systems and control from Politecnico di Milano in 2014. His research is focused on the complex real-time and embedded systems, with a focus on automation systems, fog and cloud computing systems. In this area, he has published over 100 peer-reviewed papers. He was awarded with the Swedish Research Council (VR) Starting grant for the project “PSI: Pervasive Self-Optimizing Computing Infrastructures (VR Swedish Research Council)”.

**Wilfried Steiner** is Director of the TTTech Labs which acts as center for strategic research and the center for IPR management within the TTTech Group. Wilfried Steiner holds a degree of Doctor of Technical Sciences and the Venia Docendi in Computer Science, both from the Vienna University of Technology, Austria. His research is focused on dependable cyber-physical systems, in particular in the following domains: automotive, space, aerospace, as well as new energy and industrial automation. Wilfried Steiner designs algorithms and network protocols with real-time, dependability, and security attributes.

**Karl-Erik Årzén** received his M.Sc. in Electrical Engineering and Ph.D. in Automatic Control from Lund University in 1981 and 1987, respectively. He was appointed as Full Professor in automatic control in 2000. He has also worked for ABB Corporate Research during 1992-1994. His research interests include cyber-physical systems, real-time systems, real-time and embedded control, control of computer systems, and cloud control. He is the vice-coordinator for the Lund part of the ELLIIT strategic research area on IT and mobile communication, co-director for WASP — the Wallenberg AI, Autonomous Systems and Software Program (the single largest research grant within Engineering Sciences in Sweden ever with a total budget of 550 million EUR), and is an elected member of the Royal Swedish Academy of Engineering Sciences.

**Ivona Brandic** is Professor for High Performance Computing Systems at the Vienna University of Technology. In 2015 she was awarded the FWF START prize, the highest Austrian award for early career researchers. Since 2016 she is a member of the Young Academy of the Austrian Academy of Sciences. Her interests comprise virtualized HPC systems, energy efficient ultra-scale distributed systems, massive-scale data analytics. She published more than 100 scientific journal, magazine and conference publications and she co-authored a textbook on federated and self-manageable Cloud infrastructures. She has served more than 70 program committees among others Supercomputing, CCGrid, EuroPar, and IPDPs.

**Atakan Aral** is a Senior Postdoctoral Fellow at the Vienna University of Technology (TU Wien). He received a dual M.Sc. degree in Computer Science and Engineering from Politecnico di Milano in 2011 and Istanbul Technical University (ITU) in 2012, and a Ph.D. degree in Computer Engineering from ITU in 2016. His research interests center around resource and reliability management for geo-distributed and virtualized computing systems such as intercloud and edge computing, as well as optimization of the edge computing architecture for AI services. ■

**Tutorial T3, 9 am - 1 pm, EDT**

## Deterministic Reactive Programming for Cyber-Physical Systems Using Lingua Franca

This tutorial presents Lingua Franca (LF), a polyglot coordination language for writing deterministic reactive programs that incorporate, and compile down to, popular mainstream programming languages such as C, C++, Python, and TypeScript. LF does not replace the languages we love, but instead augments them with a deterministic coordination layer and adds missing abstractions. LF transparently exploits parallelism without burdening the application programmer with the well-documented difficulties of achieving predictable behavior in multi-threaded and/or distributed software.

The tutorial targets attendees with a background in developing software for cyber-physical systems (CPS). We will show the workflow involved in developing a few small CPS applications using LF, and the benefits of determinism that can be achieved out of the box. For example, our custom IDE is capable of diagram synthesis, dependency analysis, and cycle detection that can help CPS developers avoid common sources of potential non-determinism in their software. Our framework also supports real-time capabilities such as deadlines and periodic timers, and includes a deterministic interface to interact with the physical world. We will also show some of the runtime capabilities of LF, including the ability to run a coordinated distributed system with little to no programming effort that conserves a semantic notion of time across different machines.

### Organizer(s) and speaker(s):

Soroush Bateni, *University of Texas at Dallas, USA*

Hokeun Kim, *Hanyang University, South Korea &*

*UC Berkeley, USA*

Edward A. Lee, *UC Berkeley, USA*

Shaokai Lin, *UC Berkeley, USA*

Marten Lohstroh, *UC Berkeley, USA*

Christian Menard, *TU Dresden, Germany*

Efsane Soyer, *UC Berkeley, USA*

### Bio:

**Soroush Bateni** is a PhD candidate in the Department of Computer Science at the University of Texas at Dallas. His current research focus is on deterministic distributed embedded systems and predictable AI.

**Hokeun Kim** is joining Hanyang University, Seoul, Korea, in fall 2021 as an assistant professor in Electronic Engineering. He received his Ph.D. degree in EECS from UC Berkeley in 2017 with a focus on IoT security. He continued research on Internet and computer security at Google. His research interests include the IoT, real-time systems, cyber-physical systems, and computer architecture.

**Edward A. Lee** has been working on embedded software systems for 40 years, and after detours through Yale, MIT, and Bell Labs, landed at Berkeley, where he is now Professor of the Graduate School in EECS. His research is focused on cyber-physical systems, where he strives to make composable, secure, and verifiable systems, with an emphasis on deterministic concurrency and predictable timing.

**Shaokai Lin** is a PhD student in the EECS department of UC Berkeley. His research interest is in applying formal methods in the design and verification of cyber-physical systems and timing-predictable hardware.

**Marten Lohstroh** recently obtained his PhD from UC Berkeley where he wrote his dissertation on reactors. He is still affiliated to Berkeley, but now as a postdoc. His work is focused on broadening the impact of reactors through Lingua Franca.

**Christian Menard** is a PhD student in the Department of Computer Science at TU Dresden in Germany. His research focuses on applying new models of computation in the field of compiler construction, with a particular focus on creating new tool flows for developing automotive applications.

**Efsane Soyer** is a junior studying computer science at UC Berkeley. ■

Industry Tutorial IT1, 9 am - 1 pm, EDT

## Scalable SoC Architecture for Edge AI Products

Deep neural networks (DNNs) are currently widely used for many artificial intelligence (AI) applications including computer vision, speech recognition, and robotics. While DNNs deliver state-of-the-art accuracy on many AI tasks, it comes at the cost of high computational complexity which presents serious scalability and performance-per-watt challenges for traditional CPU/GPU architectures.

The Intel Edge Inference Product (EIP) family of SoC(s) integrates Vision Processing Unit (VPU) IP targeting computer vision and general Deep Learning inferencing applications. Intel EIP SoC(s) offer scalable performance-per-watt needed for low power connected devices such as drones, intelligent security cameras to mid-high-performance Network Video Recorders, AI in a box and Deep Learning edge server cards.

This tutorial provides an overview of the Scalable EIP Architecture (SEA) framework developed to meet the goal of 5-10 TOPS/Watt for various form-factor EIP devices. Specifically, it will talk about state-of-art techniques adopted in SoC memory technology, general purpose compute, On-chip interconnects, power delivery/mgmt., security/virtualization, High speed IO's and chiplet disaggregation for best-in-class secure, flexible and energy-efficient EIP offering from Intel.

### Organizers and speakers:

Pawan Chhabra, *Intel*

Ajay Upadhyaya, *Intel*

### Bio:

**Pawan Chhabra** is a Director Engineering in Intel leading IOTG SOC Architecture. He has led SOC Architecture for the Edge Inference Product family and is currently responsible for leading low-cost client architecture. His knowledge spreads over a wide variety of different domains in the SOC covering Memory Technology, Interconnect, MMU, Cache/Coherency and pm to name a few. Pawan has been contributing over 18 years in the VLSI industry and has held IP and SoC Design lead positions, driving teams to first pass silicon of very successful Snapdragon products. Pawan has a B.Tech degree in Electrical Engineering from IIT Delhi India. He has 6 patents to his credit so far.

**Ajay Upadhyaya** is a Senior Director Engineering in Intel, India leading IOTG SOC Architecture. He has led IP & SOC Architecture in multiple domains ranging from Smartphones, Entry & Mid-tier Client Laptops, IOTG SoC mainly for Industrial applications & PCIE attach accelerator SOC. His knowledge spreads over multiple SoC domains primarily focusing on Networking offloads, Memory Hierarchies, System Memory Management Unit, Virtualization Technologies, dis-aggregated chiplet based product architectures, Compute sub systems. Ajay has been with the VLSI industry for last 24 areas, primarily working with a couple of startups at the start of his career and with Qualcomm, Intel in the last one decade. Ajay has a B.Tech degree in Electronics Engineering from IIT BHU Varanasi India. He has 2 patents approved. ■

Industry Tutorial IT2, 9 am - 1 pm, EDT

## Integrating Compute Acceleration Into Embedded System Design Using Vitis

### Important Notes:

- You must register separately for this tutorial through <https://www.xilinx.com/support/university/workshops/schedule.html>. A confirmation email will be sent upon receiving your registration. Please register ONLY if you are sure to attend the tutorial since the number of seats are limited due to hardware board resources.

- This tutorial will involve the use of online hardware resources located on ECELab site. The design compilation will occur on AWS instances and hence require good and stable network connection. You will use Remote Desktop (RDP) and Chrome browser. Further instructions will be sent couple of days before the tutorial. The AWS instances will have all necessary tools installed to run the labs.

- It will be hard to catch on with the tutorial in the middle. So, it is highly recommended that you join from the start. Joining in the middle is discouraged or prohibited.

### Description:

Xilinx is the inventor of the FPGA, programmable SoCs, and now, the ACAP. Our highly flexible programmable silicon, enabled by a suite of advanced software and tools, drives rapid innovation across a wide span of industries and technologies – from consumer to cars to the cloud.

The goal of this tutorial is to introduce the Xilinx Vitis software development environment for designing accelerators for embedded systems using Vitis. Vitis supports C/C++ and OpenCL.

Attendees will have the opportunity to learn how to use these tools, test the tutorial examples on the target boards, and understand how to build their own custom embedded systems.

### Topics to be covered:

- Xilinx Vitis development framework and design flows

- Vitis HLS project creation flow, profiling and design analysis

- Integrating Vitis HLS developed IP using Vivado IPI

- Exporting generated hardware to Vitis embedded software development flow (including Linux and Python)

- Introduction to a composable pipeline architecture

### Organizers and speakers:

Parimal Patel, *Xilinx University Program*

### Target Audience:

Embedded hardware and software developers. This is an introductory tutorial, but it is expected that attendees have some programming experience and basic understanding of computer architecture.

Xilinx will provide remote access to cloud instances which will be enabled with Xilinx tools. Attendees will also be provided hardware board access either remotely or locally. Attendees must have their own laptop with reasonable screen size to effectively try the tutorials. (Tablet, and Netbook type devices may not be suitable).

### Bio:

**Parimal Patel** received Ph.D. in Electrical and Computer Engineering from the University of Texas at Austin, Texas in 1986 before joining the University of Texas at San Antonio as an Assistant Professor. He was a Full Professor before joining Xilinx. Parimal has always enjoyed teaching and developing new courses. He has been with Xilinx for over 20 years developing new courses, updating current courses, and delivering workshops worldwide. He is actively engaged in providing training in the areas of High-Level Synthesis, Embedded Systems, DSP Design Flow, Dynamic Partial Reconfiguration, Python Productivity on Zynq (PYNQ), and Accelerated Cloud Computing on AWS with Vitis to list a few. ■

Industry Tutorial IT3, **9 am - 1 pm, EDT**

## GPU Code Generation from MATLAB – Virtual Lab

### Requirements (Who Should Attend):

Engineers experienced in MATLAB with a need to deploy algorithms to a GPU for acceleration in MATLAB or a stand-alone system. Knowledge of CUDA and/ or GPU architectures is not required but may be useful.

Each engineer should have a computer, access to a network, and a sufficiently large monitor. It's recommended to have a resolution of greater than 2048×1536. A simple laptop screen will not be enough. Having a separate screen for the WebEx is ideal, though not necessary. No GPU is required. The virtual lab will be run virtually through WebEx and the tools will be provided with GPU-enabled instances of MATLAB Online. MATLAB Online recommends using the Chrome internet browser.

See this link for recommended browsers:

<https://www.mathworks.com/support/requirements/browser-requirements.html>

### Description:

Learn how to generate CUDA code automatically from MATLAB to run on NVIDIA desktop and embedded GPUs. MATLAB is the ideal environment for exploring, developing, and prototyping algorithms. GPUs are the

hardware of choice for many applications, such as signal, image processing, and deep learning, that benefit from the parallel processing they offer. GPU Coder offers a direct route to transition from MATLAB development to deployment on GPUs via the generation of CUDA code.

This virtual lab will guide you through hands-on exercises design to ramp you up quickly on GPU Coder. Through these exercises, you will experience a typical workflow that can then be applied to your projects.

- Prototype and accelerate implementations with automatic CUDA code generation

- Enhance performance through code refactoring and design pattern pragmas

- Generate CUDA from deep learning networks for acceleration and implementation

- Deploy generated code to desktop and embedded GPUs

### Organizers and speakers:

Jack Ferrari, *The MathWorks, USA*

### Bio:

**Jack Ferrari** is a product marketing engineer focused on supporting a group of code generation tools, including GPU Coder, at MathWorks. Jack holds a bachelor's degree in Mechanical Engineering from Boston University. ■

# EDUCATION CLASSES

Saturday & Sunday, October 09-10

## SATURDAY CLASSES

**Sat, Oct 09, 2021**

**9 am - 11 am, EDT**

**A1. Edge AI Systems,**

by Prof. Lin Wang,

*VU Amsterdam*

**A2. Memory-Centric Computing,**

by Prof. Onur Mutlu,

*ETH Zurich and CMU*

**A3. Learn to Drive (and Race!) Autonomous Vehicles,**

by Prof. Rahul Mangharam,

*University of Pennsylvania* and

Dr. Johannes Betz,

*University of Pennsylvania*

**Sat, Oct 09, 2021**

**11 am - 1 pm, EDT**

**B1. TinyML on Edge,**

by Prof. Vijay Janapa Reddi,

*Harvard University*

**B2. Neural Networks and Accelerator Co-design,**

by Dr. Nicolas J Fraser,

*Xilinx*

**B3: Face verification using few-shot deep learning**

by Prof. Amit Sethi, and

Abhijeet Patil, *IIT Bombay*

## SUNDAY CLASSES

**Sun, Oct 10, 2021**

**9 am - 11 am, EDT**

**C1. Spiking Neural Networks,**

by Prof. Priyadarshini Panda, *Yale*

**C2. Neural Network Accelerator Design,**

by Prof. Yu Wang,

*Tsinghua University*

**C3. Research Reproducibility in Embedded Learning,**

by Dr. Romain Jacob, *ETH Zurich*

**Sun, Oct 10, 2021**

**11 am - 1 pm, EDT**

**D1. Introduction to Neuromorphic Computing,**

by Prof. Helen Li,

*Duke University*

**D2. DNNs on FPGAs,**

by Prof. Jaesun Seo,

*Arizona State University*

**D3. Machine Learning for Manycore System Design and Optimization,**

by Prof. Jana Doppa,

*Washington State University* and Dr. Bires Kumar,

*Duke University*.

## Education Class A1, 9 am - 11 am, EDT Edge AI Systems

### Instructor:

Lin Wang, VU Amsterdam

### Abstract:

The past decade has witnessed the proliferation of various intelligent applications, such as augmented reality and autonomous driving, powered by modern AI technologies. Meanwhile, these applications, while being computation intensive, introduce new requirements including ultra-low latency and ultra-high reliability. Such a trend has incentivized a paradigm shift from centralized cloud computing to more distributed computing at the network edge. In this lecture we will talk about edge computing systems for AI-based applications. We will focus on a representative AI task called video stream analytics and perform a case study of how to design an efficient edge computing system to support

reliable, real-time video analytics. We will also briefly cover advanced topics like edge-centric programming and resource management for achieving the goal of general-purpose edge computing.

### Bio:

**Lin Wang** is an Assistant Professor in the Computer Systems section at VU Amsterdam, The Netherlands. Before he joined VU Amsterdam, he was an Athene Young Investigator of TU Darmstadt. He obtained his PhD in Computer Science from Institute of Computing Technology, Chinese Academy of Sciences and held positions in IMDEA Networks Institute, Spain, and SnT Luxembourg. He is principal investigator of the DFG Collaborative Research Center MAKI. He is generally interested in distributed systems and networking and his current research is focused on programming models and resource management for modern networked systems including edge AI systems, in-network computing, and cyber-physical systems.

## Education Class A2, 9 am - 11 am, EDT Memory-Centric Computing

### Instructor:

Onur Mutlu, ETH Zurich and CMU

### Abstract:

Computing is bottlenecked by data. Large amounts of application data overwhelm storage capability, communication capability, and computation capability of the modern machines we design today. As a result, many key applications' performance, efficiency and scalability are bottlenecked by data movement. In this lecture, we describe three major shortcomings of modern architectures in terms of 1) dealing with data, 2) taking advantage of the vast amounts of data, and 3) exploiting different semantic properties of application data. We argue that an intelligent architecture should be designed to handle data well. We show that handling data well requires designing architectures based on three key principles: 1) data-centric, 2) data-driven, 3) data-aware. We give several examples for how to exploit each of these principles to design a much more efficient and high performance computing system. We especially discuss recent research that aims to fundamentally reduce memory latency and energy, and practically enable computation close to data, with at least two promising novel directions: 1) processing using memory, which exploits analog operational properties of memory chips to perform massively-parallel operations in memory, with low-

cost changes, 2) processing near memory, which integrates sophisticated additional processing capability in memory controllers, the logic layer of 3D-stacked memory technologies, or memory chips to enable high memory bandwidth and low memory latency to near-memory logic. We show both types of architectures can enable orders of magnitude improvements in performance and energy consumption of many important workloads, such as graph analytics, database systems, machine learning, video processing. We discuss how to enable adoption of such fundamentally more intelligent architectures, which we believe are key to efficiency, performance, and sustainability. We conclude with some guiding principles for future computing architecture and system designs.

A short accompanying paper, which appeared in DATE 2021, can be found [here](https://people.inf.ethz.ch/omutlu/pub/intelligent-architectures-for-intelligent-computing-systems-invited_paper_DATE21.pdf) and serves as recommended reading: [https://people.inf.ethz.ch/omutlu/pub/intelligent-architectures-for-intelligent-computing-systems-invited\\_paper\\_DATE21.pdf](https://people.inf.ethz.ch/omutlu/pub/intelligent-architectures-for-intelligent-computing-systems-invited_paper_DATE21.pdf)

### Bio:

**Onur Mutlu** is a Professor of Computer Science at ETH Zurich. He is also a faculty member at Carnegie Mellon University, where he previously held the Strecker Early Career Professorship. His current broader research interests are in computer architecture, systems, hardware security, and bioinformatics. A variety of techniques he, along with his group and collaborators, has invented over the years have influenced industry and have been employed in commercial microprocessors and memory/storage systems. He obtained his PhD and MS in ECE from the University of Texas at Austin and BS degrees in Computer

Engineering and Psychology from the University of Michigan, Ann Arbor. He started the Computer Architecture Group at Microsoft Research (2006-2009), and held various product and research positions at Intel Corporation, Advanced Micro Devices, VMware, and Google. He received the IEEE High Performance Computer Architecture Test of Time Award, the IEEE Computer Society Edward J. McCluskey Technical Achievement Award, ACM SIGARCH Maurice Wilkes Award, the inaugural IEEE Computer Society Young Computer Architect Award, the inaugural Intel Early Career Faculty Award, US National Science Foundation CAREER Award, Carnegie Mellon University Ladd Research Award, faculty partnership awards from various companies, and a healthy number of best paper or “Top Pick” paper recognitions at various computer systems, architecture, and security

venues. He is an ACM Fellow “for contributions to computer architecture research, especially in memory systems”, IEEE Fellow for “contributions to computer architecture research and practice”, and an elected member of the Academy of Europe (Academia Europaea). His computer architecture and digital logic design course lectures and materials are freely available on YouTube (<https://www.youtube.com/OnurMutluLectures>), and his research group makes a wide variety of software and hardware artifacts freely available online (<https://safari.ethz.ch/>). For more information, please see his webpage at <https://people.inf.ethz.ch/omutlu/>.

## Education Class A3, 9 am - 11 am, EDT Learn to Drive (and Race!) Autonomous Vehicles

### Instructor:

Dr. Rahul Mangharam, *University of Pennsylvania* and Dr. Johannes Betz, *University of Pennsylvania*

### Website:

<https://f1tenth.org>

### Abstract:

If you are interested in learning the foundations of autonomous driving, then this course is for you. But don't be worried that this is another theory-only lecture: In this lecture, we will work hands-on with everyone who is interested in the fields of motion planning, control theory, and applied machine learning. From the very beginning we will introduce you to both a simulation environment and real hardware: Our 1/10th-scale autonomous race car called F1TENTH.

First, we will teach you the fundamentals of autonomous driving in the fields of perception, planning and control and how to program them. We highlight three specific capabilities for streamlined algorithm development, testing and validation: a set of simulators, control and verification, and efficient machine-learning algorithm development. We will also show you how to bring an example autonomous driving algorithm to live in both the simulation environment and on the real F1TENTH hardware, an easy-to-use high-

performance autonomous racing platform for developing and deploying autonomous driving algorithms.

F1TENTH has a growing community of over 60 universities, 9 international autonomous racing competitions and hands-on course offerings in over a dozen institutions. In addition, by focusing on the racing environment you will also learn how to develop algorithms that operate on the edge of vehicle dynamics: High accelerations, high velocities and high computation frequencies.

The lecture will be delivered in a manner so that engineering and CS students both on undergraduate and graduate level can understand the material. We will highlight pathways to take your research forward in perception, planning and control for autonomous systems.

### Bio:

**Rahul Mangharam** leads xLAB for Safe Autonomous System in the Dept. of Electrical & Systems Engineering and Dept. of Computer & Information Science at the University of Pennsylvania. His interests are in cyber-physical systems at the intersection of formal methods, machine learning and controls. He is the Penn Director for the Department of Transportation's \$14MM Mobility21 National University Transportation Center which focuses on technologies for safe and efficient movement of people and goods. Rahul received the 2016 US Presidential Early Career Award (PECASE) from President Obama for his work on Life-Critical Systems. He also received the 2016 Department of Energy's CleanTech Prize (Regional), the 2014 IEEE Benjamin Franklin Key Award, 2013 NSF CAREER Award, 2012 Intel Early Faculty Career Award and was selected by the National Academy of Engineering for the

2012 and 2017 US Frontiers of Engineering. He has won several ACM and IEEE best paper awards.

**Johannes Betz** is a postdoctoral researcher at the University of Pennsylvania's xLab for Safe Autonomous Systems. His research focuses on holistic software development for autonomous systems at the dynamic limits in extreme and

unknown environments. By using modern algorithms from the field of artificial intelligence he is developing new and advanced methods and intelligent algorithms. Based on his additional studies in philosophy he extends current path and behavior planners to ethical autonomous systems.

## Education Class B1, 11 am – 1 pm, EDT TinyML on Edge

### Instructor:

Vijay Janapa Reddi, *Harvard University*

### Abstract:

Tiny machine learning (TinyML) is a fast-growing field at the intersection of ML algorithms and low-cost embedded systems. TinyML enables on-device analysis of sensor data (vision, audio, IMU, etc.) at ultra-low-power consumption (<1mW). Processing data close to the sensor allows for an expansive new variety of always-on ML use-cases that preserve bandwidth, latency, and energy while improving responsiveness and maintaining privacy. Yet, there are still numerous challenges to address. Tight memory and storage constraints (KBs not MBs), hardware/software heterogeneity, and a lack of relevant large-scale datasets still pose a substantial barrier to developing TinyML applications. This lecture introduces attendees to the fundamental concepts associated with TinyML. It summarizes state-of-the-art approaches, ranging from model design to deploying them efficiently on embedded hardware, highlighting the challenges and opportunities for things in-between. The lecture presents a macroscopic view of the end-to-end ML workflow, rather than focus on any part in isolation to provide a comprehensive systems-level perspective on TinyML. Attendees walk out of the virtual classroom understanding why the future of ML is tiny and bright. Join the 50,000+ TinyML learners that are a part of this journey and help define its future!

### Bio:

I am an Associate Professor in the John A. Paulson School of Engineering and Applied Sciences (SEAS) at Harvard

University. Prior to joining Harvard University, I was an Associate Professor at The University of Texas at Austin from 2011 to 2018. I started at Harvard University in the Spring of 2019.

My research is centered on mobile and edge-centric computing systems with a rare taste for cloud computing aspects, mostly as it pertains to edge computing or my students' interests. I direct the Edge Computing Lab. I believe in solving computing problems, rather than associating myself with a particular domain or field of computing (i.e., hardware or software). I take great pride in that, and that reflects in my research groups' training. Having said that, I publish in Computer Architecture and Robotics venues.

My teaching focuses on both hardware and software. At the freshman/sophomore level, I teach topics that are related to embedded systems and help explain their relationship to the rest of the connected world (i.e., the Internet of Things). At the junior and senior undergraduate level, I teach Computer Architecture. Going beyond that, at the graduate level, I teach courses that are focused on several edge computing aspects, which covers a variety of state-of-the-art research challenges and issues. Examples include how we design better systems for robotics, autonomous cars, drones, etc.

### Relevant reading:

Widening Access to Applied Machine Learning with TinyML (<https://arxiv.org/pdf/2106.04008.pdf>). Interested in learning more? Take the HarvardX TinyML course for free: <https://www.edx.org/professional-certificate/harvardx-tiny-machine-learning>

Education Class B2, 11 am – 1 pm, EDT

## Neural Networks and Accelerator Co-Design

### Instructor:

Dr. Nicolas J Fraser, Xilinx

### Abstract:

Machine learning algorithms have been gradually displacing traditional programming techniques across multiple domains, including domains that require low-latency and high-throughput, such as telecommunications and networking. Neural networks designed for these applications may require specialised accelerators in order to meet the constraints of their deployment environment. During this talk, we will discuss various forms of

specialisations that have been leveraged by the industry with their impact on potential applications, flexibility, performance and efficiency. Furthermore, we will discuss how the specialization in hardware architectures can be automated through end-to-end tool flows.

### Bio:

**Nicholas J. Fraser** received the PhD degree at The University of Sydney, Australia in 2020. Currently he's a research scientist at Xilinx Research Labs, Dublin, Ireland. His main research interests include: training of reduced precision neural networks, software / hardware co-design of neural network topologies / accelerators, and audio signal processing.

Education Class B3, 11 am – 1 pm, EDT

## Face Verification using Few-shot Deep Learning

### Instructor:

Prof. Amit Sethi, and Abhijeet Patil,

IIT Bombay

### Abstract:

In this tutorial, we are going to deploy the popular face recognition algorithm FaceNet on a Jetson Nano Developer Kit. Firstly, we will talk about few-shot learning and the methodology used to train FaceNet. We will go through basic building blocks such as metric learning, triplet loss and the training procedure of FaceNet. After understanding the working of FaceNet, we will jump to hardware deployment of face recognition. We will train FaceNet using pyTorch, then we will convert the trained model to half precision (FP16) using TensorRT. We will also demonstrate camera integration to Jetson Nano. After completing all the steps, we will have a working prototype of a face recognition system ready on a portable Jetson Nano device.

### Bio:

**Amit Sethi** is a Professor of Electrical Engineering at IIT Bombay, and a Visiting Instructor of Pathology at UIC. His research group works on computer vision, deep learning, and medical image analysis. His current research is focused on extracting valuable information, such as for prognosis, using deep learning on inexpensive medical modalities. He obtained his PhD in Electrical and Computer Engineering from University of Illinois at Urbana-Champaign with a focus on computer vision and machine learning, and bachelors in Electrical Engineering from IIT Delhi.

**Abhijeet Patil** is a PhD student at IIT Bombay, and a deep learning engineer at Griffyn Robotech – a startup working with embedded systems, robotics and deep learning in Pune India. His research interest include deep learning, computational pathology, embedded systems, object detection, tracking, and color normalization. ■

## Education Class C1, 9 am - 11 am, EDT Spiking Neural Networks

**Instructor:**

Priyadarshini Panda, *Yale*

**Abstract:**

Spiking Neural Networks (SNNs) have recently emerged as an alternative to deep learning due to their huge energy efficiency benefits on neuromorphic hardware. In this presentation, we suggest important techniques for training SNNs which bring a huge benefit in terms of latency, accuracy, interpretability, and robustness. We will first delve into how training is performed in SNNs. Training SNNs with surrogate gradients presents computational benefits due to short latency and is also considered as a more bio-plausible approach. However, due to the non-differentiable nature of spiking neurons, the training becomes problematic and surrogate methods have thus been limited to shallow networks compared to the conversion method. To address this training issue with surrogate gradients, we will also go over a recently proposed method Batch Normalization Through Time (BNTT) that allows us to target interesting beyond traditional image classification applications like video segmentation. with SNNs. Another critical limitation of

SNNs is the lack of interpretability. While a considerable amount of attention has been given to optimizing SNNs, the development of explainability still is at its infancy. I will talk about our recent work on a bio-plausible visualization tool for SNNs, called Spike Activation Map (Sam) compatible with BNTT training. The proposed Sam highlights spikes having short inter-spike interval, containing discriminative information for classification. Finally, with proposed BNTT and Sam, I will highlight the robustness aspect of SNNs with respect to adversarial attacks. In the end, I will talk about interesting prospects of SNNs for non-conventional learning scenarios such as, federated and distributed learning.

**Bio:**

**Priya Panda** is an assistant professor in the electrical engineering department at Yale University, USA. She received her B.E. and Master's degree from BITS, Pilani, India in 2013 and her PhD from Purdue University, USA in 2019. During her PhD, she interned in Intel Labs where she developed large scale spiking neural network algorithms for benchmarking the Loihi chip. She is the recipient of the 2019 Amazon Research Award. Her research interests include- neuromorphic computing, deep learning and algorithm-hardware co-design for robust and energy efficient machine intelligence.

## Education Class C2, 9 am - 11 am, EDT Neural Network Accelerator Design

**Instructor:**

Yu Wang, *Tsinghua University*

**Abstract:**

We have witnessed the rapid growth of Deep Neural Networks (DNNs) in the past decade. Deep neural network enabling technology has made a great impact in almost every field of our lives, including automatic driving, health care, smart city, social network, and so on. There are various kinds of DNNs, among which Convolutional Neural Networks (CNNs) and Recurrent Neural Networks (RNNs) are the most popular ones. CNNs have popularized image classification and object detection, while RNNs are used in natural language processing, time series applications, and sentiment analysis. Recently, Graph Neural Networks (GNNs) excel for their capability to generate high-quality node feature vectors (embeddings)

using graph-based deep learning method. GNNs are widely applied in recommendation system, social network, and biomedicine.

However, the high computation and storage complexity of neural network inference poses great difficulty on its application. Besides, the ultra-sparsity of GNNs brings great challenges to the computation on the traditional general-purpose platforms, such as CPUs and GPUs. In the past seven years, both academia and industry have devoted a lot of efforts to design Domain Specific Accelerators (DSAs) for DNN applications, so as to achieve low power and high performance deep neural network inference acceleration.

This talk will first give some basic concepts of DNN models, including CNNs, RNNs, and GNNs, from the perspective of algorithm. Secondly, the basic ideas and methodologies of designing DSAs for DNN applications will be introduced. Specifically, this talk will focus on the FPGA based neural network accelerator designs. Thirdly, some design principles of accelerating GNNs on GPUs and FPGAs will be discussed. Finally, this talk will outline the history and developing trend of DNN accelerators.

## Bio:

**Dr. Yu Wang** is a tenured professor in the Department of Electronic Engineering at Tsinghua University. He is now the Chair of the Department of Electronic Engineering and the Dean of Institute for Electronics and Information Technology in Tianjin at Tsinghua University. He has published more than 70 journals (51 IEEE/ACM journals) and 200 conference papers (15 DAC, 14 DATE, 7 ICCAD, 31 ASP-DAC, 9 FPGA) in the areas of EDA, FPGA, VLSI Design, and Embedded Systems. He has received Best Paper Award in ASP-DAC19, FPGA17, NVMSA17, ISVLSI12, Best Poster Award in HEART12, and 10 Best Paper Nominations. He is a recipient of ACM/SIGDA Meritorious Service Award in 2020, Under-40 Innovators Award at DAC in 2018 (5 all over the world/year), IBM X10 Faculty Award in 2010 (one of 30 worldwide). He is the co-founder of Deephi Tech (a leading

deep learning solution provider), which is acquired by Xilinx in 2018. He served as TPC chair for ISVLSI 2018, Program Co-Chair for ICFPT 2019/2011 and Finance Chair of ISLPED 2012-2016, Track Chair for DATE 2017-2019 and GLVLSI 2018, General Chair Secretary for ASP-DAC 2020, Executive Committee Member for DAC 2020, PC member for leading conferences in these areas. He also served as Co-Editor-in-Chief for ACM SIGDA E-News in 2017-2019, Associate Editor for Journal of Circuits, Systems, and Computers in 2013-2020, and Special Issue Editor for Microelectronics Journal in 2017-2019. Currently he serves as Associate Editor for IEEE TCAD, IEEE TCSV, ACM TECS, ACM TODAES, IET Computers and Digital Techniques, IEEE Embedded System Letter. He is an ACM/IEEE Senior Member.

## Education Class C3, 9 am - 11 am, EDT Research Reproducibility in Embedded Learning

### Instructor:

Romain Jacob, ETH Zurich

### Abstract:

When designing their performance evaluations, researchers often encounter questions such as: How long should a run be? How many runs to perform? How to account for the variability across multiple runs? What statistical methods should be used to analyze the data? Despite the best intentions, researchers often answer these questions differently, thus impairing the replicability of evaluations and the confidence in the results.

Improving the standards of replicability in embedded systems has recently gained traction within the community. As an important piece of the puzzle, we have developed a systematic methodology that streamlines the design and analysis of performance evaluations, and we have implemented this methodology into a framework called TriScale.

This lecture introduces the main concepts of the methodology and lets you experiment with TriScale. By the end of the lecture, you will be able to:

- Understand the difference between replicability and reproducibility, and why these notions matter;

- Understand why performance evaluation experiments must be replicable to be meaningful;

- Understand the basics of statistics required to assess replicability;

- Answer questions such as “How many times should I repeat my experiment?” rationally;

- Use the TriScale framework to help you design your next experiments, analyze your data, and report your results in a (more) replicable fashion.

The methods and principles underlying TriScale are broadly applicable to performance evaluations in (embedded) systems and networking, including simulations, emulations, and experiments on physical hardware platforms. Throughout the lecture, we draw on networked embedded systems use cases to illustrate the main concepts. Finally, we conclude with a note on the replicability challenges for machine learning, and how TriScale may help to address those as well.

### Bio:

**Roman Jacob** is postdoctoral researcher at ETH Zurich in the group of Prof. Laurent Vanbever. His current research interests are focused on computer networks, communication protocols, (real-time) scheduling theory, and statistics applied to experimental design. He started to work on TriScale from his own need to design sound performance evaluations for low-power wireless communication protocols, which was the topic of his doctoral dissertation, supervised by Prof. Lothar Thiele. At the time, he has been heavily involved in the IoTBench initiative, which aims at designing benchmarks for low-power wireless; and as he learned then, there can be no proper benchmarking without replicability! So here he is.

Education Class D1, 11 am – 1 pm, EDT

## Introduction to Neuromorphic Computing

Instructor:

Helen Li, *Duke University*

### Abstract:

The human brain is the most sophisticated organ that nature ever builds. Building a machine that can function like a human brain, indubitably, is the ultimate dream of a computer architect. Although we have not yet fully understood the working mechanism of human brains, the part that we have learned in the past seventy years already guided us to many remarkable successes in computing applications, e.g., artificial neural networks and machine learning. Inspired by the working mechanism of the human brain, neuromorphic system naturally possesses a massively parallel architecture with closely coupled memory, offering a great opportunity to break the “memory wall” in von Neumann architecture. The talk will start with a background introduction of neuromorphic computing, followed by examples of hardware acceleration schemes of learning and neural network algorithms and memristor-based computing engine. I will also share our prospects on the future technology challenges and advances of neuromorphic computing.

### Bio:

**Hai (Helen) Li** received her bachelor's and master's degrees from Tsinghua University, China, and her Ph.D. degree from Purdue University, USA. She is Clare Boothe Luce Professor and Associate Chair of the Electrical and Computer Engineering Department at Duke University. Before that, she was with Qualcomm Inc., San Diego, CA, USA, Intel Corporation, Santa Clara, CA, Seagate Technology, Bloomington, MN, USA, the Polytechnic Institute of New York University, Brooklyn, NY, USA, and the University of Pittsburgh, Pittsburgh, PA, USA. Her research interests include neuromorphic computing systems, machine learning and deep neural networks, memory design and architecture, and cross-layer optimization for low power and high performance. She has authored or co-authored more than 250 technical papers in peer-reviewed journals and conferences and a book entitled *Nonvolatile Memory Design: Magnetic, Resistive, and Phase Changing* (CRC Press, 2011). She received 9 best paper awards and an additional 9 best paper nominations from international conferences. Dr. Li serves/served as an Associate Editor of a number of IEEE/ACM journals. She was the General Chair or Technical Program Chair of multiple IEEE/ACM conferences. Dr. Li is a Distinguished Lecturer of the IEEE CAS society (2018-2019) and a distinguished speaker of ACM (2017-2020). Dr. Li is a recipient of the NSF Career Award, DARPA Young Faculty Award (YFA), TUM-IAS Hans Fischer Fellowship from Germany, and ELATE Fellowship (2020). Dr. Li is an IEEE fellow and a distinguished member of the ACM.

Education Class D2, 11 am – 1 pm, EDT

## DNNs on FPGAs

Instructor:

Jaesun Seo, *Arizona State University*

### Abstract:

Deep neural networks (DNNs) have been successful in many practical applications including image classification, object detection, speech recognition, etc. GPUs have been a popular hardware platform for DNN workloads, aided by highly parallel computing with a massive number of processing cores. However, due to the lack of reconfigurability and high power consumption, GPU is not an ideal accelerator solution for DNN models especially with high sparsity or customized architectures.

Application-specific integrated circuits (ASICs) typically have the highest energy efficiency, but their limited configurability can introduce a significant risk of premature obsolescence. With DNN algorithms evolving at a fast pace, ASIC designs will always lag behind the cutting edge due to the long design cycle. To that end, FPGAs have a unique advantage with potentially higher throughput and efficiency than GPUs, while offering faster time-to-market and potentially longer useful life than ASIC solutions.

In this lecture, we will present FPGA-based DNN accelerator designs and methodologies. We will first introduce the basics of DNN algorithms, and hardware requirements for computation and memory. Next, we will present efficient FPGA acceleration schemes, including loop optimization of iterative DNN operations, parallel computation, dataflow and data re-use, minimization of memory access, low-precision quantization, sparsity and

pruning, etc. The lecture will discuss the key design trade-offs to map DNN algorithms on different FPGAs and how to optimally improve the throughput, power, and energy-efficiency for target applications.

**Bio:**

**Jae-sun Seo** received the Ph.D. degree in electrical engineering from the University of Michigan in 2010. From 2010 to 2013, he was with IBM T. J. Watson Research Center, where he worked on cognitive computing chips under the

DARPA SyNAPSE project and energy-efficient integrated circuits for high-performance processors. In 2014, he joined ASU in the School of ECEE, where he is now an Associate Professor. During the summer of 2015, he was a visiting faculty at Intel Circuits Research Lab. His research interests include efficient hardware design of machine learning / neuromorphic algorithms and integrated power management. Dr. Seo was a recipient of IBM Outstanding Technical Achievement Award (2012), NSF CAREER Award (2017), and Intel Outstanding Researcher Award (2021).

## Education Class D3, 11 am – 1 pm, EDT Machine Learning for Manycore System Design and Optimization

**Instructor:**

Bires Kumar, *Duke University* and Jana Doppa, *Washington State University*

**Abstract:**

Advanced computing systems have long been enablers for breakthroughs in science and engineering applications including Artificial Intelligence (AI) and Machine Learning (ML) either through sheer computational power or form-factor miniaturization. However, as algorithms become more complex and the size of datasets increase, existing computing platforms are no longer sufficient to bridge the gap between algorithmic innovation and hardware design due to nearing the end of Moore's law. This educational lecture will focus on how manycore systems designed by leveraging the benefits of emerging technologies (e.g., three-dimensional integration, processing-in-memory) and machine learning have the potential to bridge this growing gap. First, we will provide the basics on manycore systems — compute layer, interconnect layer, and memory layer — and discuss the challenges of data movement. Second, we will discuss the advantages of heterogeneous computing, 3D integration, and processing-in-memory in addressing the data movement challenge. Third, we will explain the challenges of application-specific manycore systems design due to large combinatorial spaces and the need to perform expensive simulations to optimize multiple conflicting objectives (e.g., power, performance, and temperature). Fourth, we will describe how machine learning can enable efficient and accurate manycore systems design

optimization. Finally, we will discuss hardware and software co-design methodologies for emerging deep learning applications.

The lecture will be delivered in a way that any undergraduate student from ECE or CS can understand the material. No background on manycore systems or machine learning is assumed.

**Bio:**

**Jana Doppa** is the George and Joan Berry Distinguished Associate Professor in the School of Electrical Engineering and Computer Science at Washington State University, Pullman. He received his Ph.D. degree in Computer Science from Oregon State University and his M.Tech. degree from Indian Institute of Technology (IIT), Kanpur. His primary research focus is at the intersection of machine learning and electronic design automation by exploring the synergies between these two mutually beneficial areas.

His research has been recognized with a number of awards, honors, and distinctions including the 2019 National Science Foundation CAREER Award; the 2021 Early Career Award in AI by the International Joint Conference on Artificial Intelligence for ML algorithms to accelerate design automation for science and engineering applications including electronic design automation; the 2021 Best Paper Award from ACM Transactions on Design Automation of Electronic Systems; the 2013 Outstanding Paper Award from the AAAI Conference on Artificial Intelligence; the 2018 Best Student Abstract Award from the AAAI Conference on Artificial Intelligence; the 2015 Outstanding PhD Dissertation Award from Oregon State University and was nominated for ACM Doctoral Dissertation Award; a 2015 Google Faculty Research Award; the 2013 Outstanding Graduate Student Award from College of Engineering, Oregon State University; the 2020 Outstanding Junior Faculty Research Award and the 2018 Reid-Miller Teaching Excellence Award from the College of Engineering, Washington State University.

# SUNDAY, OCTOBER 10 - EDUCATION

---

**Biresh Kumar Joardar** is an NSF sponsored Computing Innovation Fellow (postdoctoral researcher) in Electrical and Computer Engineering at Duke University mentored by Prof. Krishnendu Chakrabarty. He received his Ph.D. degree in Computer Engineering from Washington State University and his BE degree in ECE from Jadavpur University. His primary research is at the intersection of manycore systems design and machine learning with a current focus on reliable ML on unreliable hardware.

His research has been recognized with a number of awards, honors, and distinctions including a 2021 DAAD AI-net Fellowship; a 2020 NSF Computing Innovation Fellowship; the 2019 Best Paper Award at NOCS; Nominated for Best Paper Award at DATE-2020 and DATE-2021 conferences; the 2019 Outstanding Graduate Student Researcher Award from the College of Engineering, WSU; and the 2018 Harold and Dianna Frank Electrical Engineering Fellowship, WSU. ■

# MONDAY PROGRAM

## October 11

|                        |                                                                                                                                 |                                                                                           |                                                                                             |                                                                                                                               |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 9:30 am -<br>9:55 am   | <b>ESWEEK Opening</b>                                                                                                           |                                                                                           |                                                                                             |                                                                                                                               |