Association for

Computing Machinery

IEEE

Updated August 1

ISLPED 2024

# INTERNATIONAL SYMPOSIUM ON LOW POWER ELECTRONICS AND DESIGN

AUGUST 5–7, 2024, NEWPORT BEACH, CA, USA

Silver Sponsor

Bronze Sponsor

IEEE Council on Electronic Design Automation

IEEE CIRCUITS AND SYSTEMS SOCIETY

IEEE

Solid-State

Circuits Society™

IC Innovation

# LOGISTICS

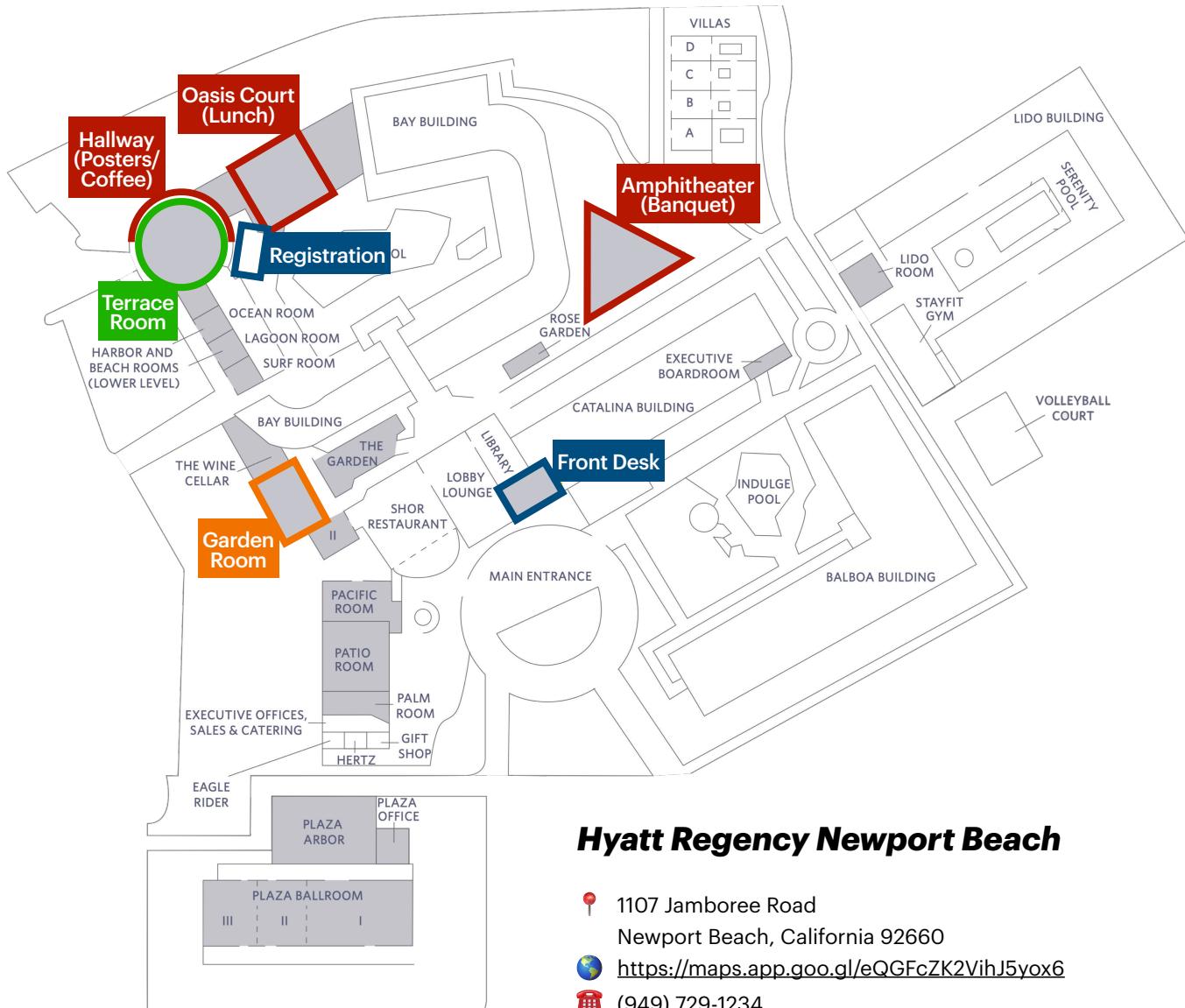

## Hyatt Regency Newport Beach

- 📍 1107 Jamboree Road

Newport Beach, California 92660

- 🌐 <https://maps.app.goo.gl/eQGFcZK2VihJ5yox6>

- ☎️ (949) 729-1234

- 🏡 [newportbeach.hyatt.com](http://newportbeach.hyatt.com)

Network: Hyatt\_Meetings

Password: Meetings24

# PROGRAM OVERVIEW

T Terrace Room G Garden Room

|                            |             |                                                                                                                                        |                                                                                                                      |

|----------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| <b>Monday, August 5</b>    | 7:30–8:00   | <b>Registration</b>                                                                                                                    |                                                                                                                      |

|                            | 8:00–8:30   | <b>Welcome</b> T                                                                                                                       |                                                                                                                      |

|                            | 8:30–9:30   | <b>Keynote 1</b> T<br><b>Behzad Razavi, UCLA</b> "Power Consumption Bounds in Wireline Transceivers"                                   |                                                                                                                      |

|                            | 9:30–10:00  | Coffee Break (Hallway)                                                                                                                 |                                                                                                                      |

|                            | 10:00–11:40 | <b>Session 1A</b> T<br>"Transformers and Natural Language Processing"                                                                  | <b>Session 1B</b> G<br>"Energy- and Carbon-efficient Machine Learning Techniques"                                    |

|                            | 11:40–12:20 | <b>Design Contest</b> T                                                                                                                |                                                                                                                      |

|                            | 12:20–13:40 | <b>Lunch</b> (Oasis Court)                                                                                                             |                                                                                                                      |

|                            | 13:40–15:00 | <b>Panel Discussion</b> T<br><b>Massoud Pedram, USC</b> "Balancing Accuracy, Trust, and Efficiency in Edge AI: Is There a Sweet Spot?" |                                                                                                                      |

|                            | 15:00–16:40 | <b>Session 2A</b> T<br>"Energy-Efficient Neural Networks via Algorithm-Hardware Co-optimization"                                       | <b>Session 2B</b> G<br>"Eye for the Detail: Bringing Security and Privacy to Nanoscale Systems"                      |

|                            | 7:30–8:00   | <b>Registration</b>                                                                                                                    |                                                                                                                      |

| <b>Tuesday, August 6</b>   | 8:00–9:00   | <b>Keynote 2</b> T<br><b>Vivek De, Intel</b> "Attack-Resistant Energy-Efficient SoCs for Smart and Secure Cyberphysical Systems"       |                                                                                                                      |

|                            | 9:00–9:30   | Coffee Break (Hallway)                                                                                                                 |                                                                                                                      |

|                            | 9:30–11:10  | <b>Session 3A</b> T<br>"Emerging AI Accelerator Design"                                                                                | <b>Session 3B</b> G<br>"Advances in Power Modeling and Low Power Design Methods"                                     |

|                            | 11:10–12:30 | <b>Special Session</b><br>"Low-power Heterogeneous Integration Platforms"                                                              |                                                                                                                      |

|                            | 12:30–13:40 | <b>Lunch</b> (Oasis Court)                                                                                                             |                                                                                                                      |

|                            | 13:40–14:10 | <b>Poster Pitch</b> T                                                                                                                  |                                                                                                                      |

|                            | 14:10–15:10 | <b>Poster Session</b> (Hallway, with coffee)                                                                                           |                                                                                                                      |

|                            | 15:10–17:15 | <b>Session 4A</b> T<br>"Next Generation Memories and Wearables"                                                                        | <b>Session 4B</b> G<br>"Optimizing Data Movement in Diverse Architectures: from VLIW to Optical Baseband Processors" |

|                            | 18:00–20:30 | <b>Banquet</b> (Amphitheater)                                                                                                          |                                                                                                                      |

|                            | 7:30–8:00   | <b>Registration</b>                                                                                                                    |                                                                                                                      |

| <b>Wednesday, August 7</b> | 8:00–9:00   | <b>Keynote 3</b> T<br><b>Kyomin Sohn, Samsung</b> "Memory Solutions for On-device AI"                                                  |                                                                                                                      |

|                            | 9:30–9:30   | Coffee Break (Hallway)                                                                                                                 |                                                                                                                      |

|                            | 9:30–11:10  | <b>Session 5</b> T<br>"Power Management and Energy Efficiency in AI Hardware Design"                                                   |                                                                                                                      |

|                            | 11:10–12:25 | <b>Session 6</b> T<br>"Energy-Efficient Adaptive Internet-of-Things Systems"                                                           |                                                                                                                      |

|                            | 12:25–12:50 | <b>Closing Remarks and Awards</b> T                                                                                                    |                                                                                                                      |

# MONDAY TECHNICAL PROGRAM

|                    |                                                                                                                                                                                                                          |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>8:30–9:30</b>   | <b>Keynote 1</b>                                                                                                                                                                                                         |

| <b>Terrace</b>     | Chair: Pascal A. Meinerzhagen, Intel                                                                                                                                                                                     |

|                    | <b>Power Consumption Bounds in Wireline Transceivers</b><br>Behzad Razavi, UCLA                                                                                                                                          |

| <b>10:00–11:40</b> | <b>Session 1A: “Transformers and Natural Language Processing”</b>                                                                                                                                                        |

| <b>Terrace</b>     | Chair: Dolly Sapra, University of Amsterdam                                                                                                                                                                              |

| 10:00–10:25        | <b>A 28nm Scalable and Flexible Accelerator for Sparse Transformer Models (Best Paper Candidate)</b><br>Yuan Liao, Jian Meng and Jae-sun Seo                                                                             |

| 10:25–10:50        | <b>Hyft: A Reconfigurable Softmax Accelerator with Hybrid Numeric Format for both Training and Inference</b><br>Tianhua Xia and Sai Qian Zhang                                                                           |

| 10:50–11:15        | <b>PEANO-ViT: Power-Efficient Approximations of Non-Linearities in Vision Transformers</b><br>Mohammad Erfan Sadeghi, Arash Fathyazi, Seyedarmin Azizi and Massoud Pedram                                                |

| 11:15–11:40        | <b>Heterogeneous Memory Integration and Optimization for Energy-Efficient Multi-Task NLP Edge Inference</b><br>Zirui Fu, Aleksandre Avaliani and Marco Donato                                                            |

| <b>10:00–11:40</b> | <b>Session 1B: “Energy- and Carbon-efficient Machine Learning Techniques”</b>                                                                                                                                            |

| <b>Garden</b>      | Chair: Kangmin Lee, Google                                                                                                                                                                                               |

| 10:00–10:25        | <b>LUTIN: Efficient Neural Network Inference with Table Lookup</b><br>Shi-Zhe Lin, Yun-Chih Chen, Yuan-Hao Chang, Tei-Wei Kuo and Hsiang-Pang Li                                                                         |

| 10:25–10:50        | <b>CLOVER: Carbon Optimization of Federated Learning over Heterogeneous Clients (Best Paper Candidate)</b><br>Chanwoo Cho, Yonglak Son, Seongbin Park and Young Geun Kim                                                 |

| 10:50–11:15        | <b>Xyloni: Very Low Power Neural Network Accelerator for Intermittent Remote Visual Detection of Wildfire and Beyond</b><br>Jeffrey Chen, Sang-Woo Jun, Aditi Mundra and Jonathan Ta                                     |

| 11:15–11:40        | <b>EA<sup>2</sup>: Energy Efficient Adaptive Active Learning for Smart Wearables</b><br>Hamidreza Alikhani Koshkak, Ziyu Wang, Anil Kanduri, Pasi Liljeberg, Amir M. Rahmani and Nikil Dutt                              |

| <b>11:40–12:20</b> | <b>Design Contest</b>                                                                                                                                                                                                    |

| <b>Terrace</b>     | Co-Chairs: Rajesh Kedia, IIT Hyderabad; Payam Heydari, University of California, Irvine                                                                                                                                  |

|                    | <b>Design and Applications of Low-Power RISC-V Multicore Processors with a Unified Lightweight FPU</b><br>Jina Park, Kyeongwon Lee, Eunjin Choi, Hyunseok Kwak, Jae-Jin Lee, Kyuseung Han, Woojoo Lee and Massoud Pedram |

|                    | <b>A Sub-1uJ/class SoC for Headset-Integrated Mind Imagery and Control in VR/MR Applications</b><br>Zhiwei Zhong, Yijie Wei, Lance Go and Jie Gu                                                                         |

**eTag: An Energy-Neutral Ear Tag for Real-Time Body Temperature Monitoring of Dairy Cattle**

Hien Vu, Hanwook Chung, Christopher Choi and Younghyun Kim

**Viewer-Aware Low-Power Mobile Video System**

Destinie Diggs, William Oswald and Na Gong

**13:40-15:00 Panel Discussion**

**Terrace** Organizer and Moderator: Massoud Pedram, University of Southern California

**Balancing Accuracy, Trust, and Efficiency in Edge AI: Is There a Sweet Spot?**

Yiran Chen, Duke University

Hadi Esmaeilzadeh, University of California San Diego

Kaushik Roy, Purdue University

Amir Salek, Cereberus Capital

Yanzhi Wang, Northeastern University

**15:00-16:40 Session 2A: “Energy-Efficient Neural Networks via Algorithm-Hardware Co-optimization”**

**Terrace** Chair: Seungkyu Choi, Kyung Hee University

15:00-15:25 **SwiSS: Switchable Single-Sided Sparsity-based DNN Accelerators**

Shamik Kundu, Soumendu Kumar Ghosh, Arnab Raha and Deepak A. Mathaikutty

15:25-15:50 **PiQi: Partially Quantized DNN Inference on HMPSoCs**

Ehsan Aghapour, Yixian Shen, Dolly Sapra, Andy Pimentel and Anuj Pathania

15:50-16:15 **STARC: Crafting Low-Power Mixed-Signal Neuromorphic Processors by Bridging SNN Frameworks and Analog Designs**

Kyuseung Han, Hyunseok Kwak, Kwang-Il Oh, Sukho Lee, HyeongUk Jang, Jae-Jin Lee and Woojoo Lee

16:15-16:40 **Sparrow ECC: A Lightweight ECC Approach for HBM Refresh Reduction towards Energy-efficient DNN Inference (Best Paper Candidate)**

Hoseok Kim, Seung Hun Choi, Young-Ho Gong, Joonho Kong and Sung Woo Chung

**15:00-16:15 Session 2B: “Eye for the Detail: Bringing Security and Privacy to Nanoscale Systems”**

**Garden** Chair: Marco Donato, Tufts University

15:00-15:25 **CIPUF: Towards On-chip Learnable Anomaly Detection with Compute-In-PUF Architecture**

Jianbo Liu, Boyang Cheng, Zephany M. Enciso, Steven Davis and Ningyuan Cao

15:25-15:50 **X-IMM: Mixed-Signal Iterative Montgomery Modular Multiplication**

Mehdi Kamal and Massoud Pedram

15:50-16:15 **Securing Deep Neural Networks on Edge from Membership Inference Attacks Using Trusted Execution Environments**

Cheng-Yun Yang, Gowri Ramshankar, Nicholas Eliopoulos, Purvish Jajal, Sudarshan Nambiar, Evan Miller, Xun Zhang, Dave (Jing) Tian, Shuo-Han Chen, Chiy-Ferng Perng and Yung-Hsiang Lu

# TUESDAY TECHNICAL PROGRAM

|                    |                                                                                                                                                                                                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>8:00–9:00</b>   | <b>Keynote 2</b>                                                                                                                                                                                                                                                     |

| <b>Terrace</b>     | Chair: Kapil Dev, Nvidia<br><br><b>Attack-Resistant Energy-Efficient SoCs for Smart and Secure Cyberphysical Systems</b><br>Vivek De, Intel                                                                                                                          |

| <b>9:30–11:10</b>  | <b>Session 3A: “Emerging AI Accelerator Design”</b>                                                                                                                                                                                                                  |

| <b>Terrace</b>     | Chair: Lei Jiang, Indiana University                                                                                                                                                                                                                                 |

| 9:30–9:55          | <b>LowPASS: A Low Power PIM-based Accelerator with Speculative Scheme for SNNs</b><br>Zongwu Wang, Fangxin Liu, Longyu Zhao, Shiyuan Huang and Li Jiang                                                                                                              |

| 9:55–10:20         | <b>Systolic Array Acceleration of Spiking Neural Networks with Application-Independent Split-Time Temporal Coding</b><br>Jeongjun Lee and Peng Li                                                                                                                    |

| 10:20–10:45        | <b>All You Need is Unary: End-to-End Unary Bit-stream Processing in Hyperdimensional Computing</b><br>Mehran Shoushtari Moghadam, Sercan Aygun, Faeze S. Banitaba and M. Hassan Najafi                                                                               |

| 10:45–11:10        | <b>An Energy-Efficient 3D Point Neural Network Accelerator with Fine-grained LiDAR-SoC Pipeline Structure (Best Paper Candidate)</b><br>Bokyoung Seo, Jueun Jung, Donghyeon Han and Kyuho Jason Lee                                                                  |

| <b>9:30–11:10</b>  | <b>Session 3B: “Advances in Power Modeling and Low Power Design Methods”</b>                                                                                                                                                                                         |

| <b>Garden</b>      | Chair: Amit Agarwal, Intel                                                                                                                                                                                                                                           |

| 9:30–9:55          | <b>3D-Aware Low Power High-level Resource Binding and Co-Design</b><br>Daniel Xing and Ankur Srivastava                                                                                                                                                              |

| 9:55–10:20         | <b>Unleashing Flexibility of ML-based Power Estimators Through Efficient Development Strategies (Best Paper Candidate)</b><br>Yao Lu, Qijun Zhang and Zhiyao Xie                                                                                                     |

| 10:20–10:45        | <b>3D IC Architecture Evaluation and Optimization with Digital Compute-in-Memory Designs</b><br>Hyung Joon Byun, Udit Gupta and Jae-sun Seo                                                                                                                          |

| 10:45–11:10        | <b>Hetero-3D: PPA and Power Delivery Benefits of Heterogeneous 3D ICs with a Customized Physical Design Flow</b><br>Lingjun Zhu, Jiawei Hu, Gauthaman Murali and Sung Kyu Lim                                                                                        |

| <b>11:10–12:30</b> | <b>Special Session: “Low-power Heterogeneous Integration Platforms”</b>                                                                                                                                                                                              |

| <b>Terrace</b>     | Organizers: Vikram Jain, University of California, Berkeley; Marina Zapater, HES-SO<br>Chairs: Vikram Jain, University of California, Berkeley; Jerald Yoo, Seoul National University                                                                                |

| 11:10–11:30        | <b>Cross-layer Exploration of 2.5D Energy-Efficient Heterogeneous Chiplets Integration: From System Simulation to Open Hardware</b><br>Anna Burdina, Gabriel Catel Torres, Davide Schiavone, Miguel Peón-Quirós, Giovanni Ansaloni, David Atienza and Marina Zapater |

| 11:30–11:50        | <b>Design Approach for Die-to-Die Interfaces to Enable Energy-Efficient Chiplet Systems</b><br>Vikram Jain, Wei Tang, Zuoguo Wu, Viansa Schmulbach, Sophia Shao, Zhengya Zhang and Borivoje Nikolic                                                                  |

| 11:50–12:10        | <b>Enabling Chiplet Integration: UCIe and the Future of Die-to-Die IO</b><br>Zuoguo Wu                                                                                                                                                                               |

|                            |                                                                                                                                                                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12:10–12:30                | <b>An Open-source Generator for Lightweight UCle D2D Interface to Enable Energy-Efficient Multi-Chiplet Systems at the Edge</b><br>Vikram Jain                                                                                       |

| <b>13:40–15:10</b>         | <b>Poster Pitch and Poster Session</b>                                                                                                                                                                                               |

| <b>Terrace and Hallway</b> | Chair: Jerald Yoo, Seoul National University                                                                                                                                                                                         |

|                            | Poster Pitch in the Terrace Room, followed by Poster Session in the Hallway<br>List of posters on p. 9                                                                                                                               |

| <b>15:10–16:50</b>         | <b>Session 4A: “Next Generation Memories and Wearables”</b>                                                                                                                                                                          |

| <b>Terrace</b>             | Chair: Sai Qian Zhang, New York University                                                                                                                                                                                           |

| 15:10–15:35                | <b>Coupled 7T 1C SRAM based In-memory Computing Architecture with Gain/Offset Error Auto-compensated SAR ADC</b><br>Honggu Kim, Yerim An and Yong Shim                                                                               |

| 15:35–16:00                | <b>Magnet Free Inductive Wireless Power and Data Transmission System For Fully Implantable Cochlear Implants (Best Paper Candidate)</b><br>Mert Doğan, Ayşe Beyhan Türkyılmaz, Yasemin Engür and Haluk Külah                         |

| 16:00–16:25                | <b>Cooling the Chaos: Mitigating the Effect of Threshold Voltage Variation in Cryogenic CMOS Memories</b><br>Rakshith Saligram, Amol Gaidhane, Yu Cao, Suman Datta and Arijit Raychowdhury                                           |

| 16:25–16:50                | <b>STT-MRAM-based Near-Memory Computing Architecture with Read Scheme and Dataflow Co-Design for High-Throughput and Energy-Efficiency</b><br>Yunho Jang, Yeseul Kim and Jongsun Park                                                |

| <b>15:10–17:15</b>         | <b>Session 4B: “Optimizing Data Movement in Diverse Architectures: from VLIW to Optical Baseband Processors”</b>                                                                                                                     |

| <b>Garden</b>              | Chair: Marco Donato, Tufts University                                                                                                                                                                                                |

| 15:10–15:35                | <b>GUMSO: Gating Unnecessary On-Chip Memory Slices for Power Optimization on GPUs</b><br>Seunghyun Jin, Hyunwuk Lee and Won Woo Ro                                                                                                   |

| 15:35–16:00                | <b>ReOVE: Restricted Out-of-Order Execution for Superscalar Processors with Vector Extension</b><br>Masayuki Kimura and Ryota Shioya                                                                                                 |

| 16:00–16:25                | <b>SPADES: A 0.54-GFLOPS/W Sparse Matrix Vector Multiplication Accelerator Featuring On-the-Fly GZIP Decompression for 3.36X Reduction in Off-Chip Data Movement</b><br>Paul Xuanyuanliang Huang, Yannis P. Tsividis and Mingoo Seok |

| 16:25–16:50                | <b>ParaBase: A Configurable Parallel Baseband Processor for Ultra-High-Speed Inter-Satellite Optical Communications</b><br>Seungkyu Choi, Huanshihong Deng, Kuan-Yu Chen, Yufan Yue, David Blaauw and Hun Seok Kim                   |

| 16:50–17:15                | <b>LOCo: LPDDR Optimization with Compression and IECC scheme for DNN Inference (Best Paper Candidate)</b><br>Jae-Youn Hong, Sungkyu Kim, Je-Woo Jang and Joon-Sung Yang                                                              |

# WEDNESDAY TECHNICAL PROGRAM

|                    |                                                                                                                                                                                |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>8:00–9:00</b>   | <b>Keynote 3</b>                                                                                                                                                               |

| <b>Terrace</b>     | Chair: Jerald Yoo, Seoul National University<br><br><b>Memory Solutions for On-device AI</b><br>Kyomin Sohn, Samsung                                                           |

| <b>9:30–11:10</b>  | <b>Session 5: “Power Management and Energy Efficiency in AI Hardware Design”</b>                                                                                               |

| <b>Terrace</b>     | Chair: Shamik Kundu, Intel                                                                                                                                                     |

| 9:30–9:55          | <b>Hardware Acceleration of Inference on Dynamic GNNs (Best Paper Candidate)</b><br>Sudipta Mondal and Sachin S. Sapatnekar                                                    |

| 9:55–10:20         | <b>iSPADE: End-to-end Sparse Architecture for Dense DNN Acceleration via Inverted-bit Representation</b><br>Dongjun Kim, Han Cho and Jongsun Park                              |

| 10:20–10:45        | <b>ePredictNet: Low Cost Error Prediction Neural Network</b><br>Georgios Chatzitsompanis and Georgios Karakonstantis                                                           |

| 10:45–11:10        | <b>Energy Harvesting-Supported Efficient Low-Power ML Processing with Adaptive Checkpointing and Intermittent Computing</b><br>Sanket Shukla and Sai Manoj Pudukotai Dinakarao |

| <b>11:10–12:25</b> | <b>Session 6: “Energy-Efficient Adaptive Internet-of-Things Systems”</b>                                                                                                       |

| <b>Terrace</b>     | Chair: Younghyun Kim, Purdue University                                                                                                                                        |

| 11:10–11:35        | <b>Rapid Hardware/Software Design Space Exploration for Efficient Intermittent Systems</b><br>Youngbin Kim and Hyoseung Kim                                                    |

| 11:35–12:00        | <b>Statues: Energy-Efficient Video Object Detection on Edge Security Devices with Computational Skipping</b><br>Yeonggeon Kim, Hyunmin Kim and Sungju Ryu                      |

| 12:00–12:25        | <b>Causes and Fixes of Unexpected Drone Shutoffs</b><br>Choi Hojun, Chanyeok Choi and Youngmoon Lee                                                                            |

# POSTERS

## # Tuesday 13:40–15:10 in Terrace and Hallway

- 1 **Energy Efficiency Through In-Sensor Computing: ADC-less Real-Time Sensing for Image Edge Detection**

Nirmoy Modak and Kaushik Roy

- 2 **FPIA: Field-Programmable Ising Arrays with In-Memory Computing**

George Hutchinson, Ethan J. Sifferman, Tinish Bhattacharya, Dongseok Kwon and Dmitri Strukov

- 3 **Cryogenic Operation of Computing-In-Memory based Spiking Neural Network**

Laith A. Shamieh, Weichun Wang, Shida Zhang, Rakshit Saligram, Amol Domaji Gaidhane, Yu Cao, Arijit Raychowdhury, Suman Datta and Saibal Mukhopadhyay

- 4 **EDeN: Enabling Low-Power CNN Inference on Edge Devices Using Prefetcher-assisted NVM Systems**

Jihoon Jang, Hyojeun Lee and Hyun Kim

- 5 **Triangle Counting in the Temporal Domain**

Caroline Ellis Hammond, Patricia Gonzalez-Guerrero, Meriam Gay Bautista and Nirmalendu Bikash Patra

- 6 **ML-INSIGHT: Machine Learning for Inrush Current Prediction and Power Switch Network Improvement**

Vikram Gopalakrishnan, Bing-Yue Wu and Vidya A. Chhabria

- 7 **HQ-DTM: A Hierarchical Q-learning Algorithm for Dynamic Thermal Management of Multi-core Processors**

Abir Ahsan Akib and Ankur Srivastava

- 8 **A Technology-Agnostic Method for Digital LDO Synthesis and Layout Automation**

Yaswanth Kumar Cherivirala and David Wentzloff

- 9 **PACT: Accurate Power Analysis and Carbon Emission Tracking for Sustainability**

Aditya Ukarande, Toygun Basaklar, Mingcong Cao and Umit Ogras

- 10 **DISHA: Low-Energy Sparse Transformer at Edge for Outdoor Navigation for the Visually Impaired Individuals**

Praveen Nagil and Sumit K. Mandal

- 11 **Content-based Power-saving Design for Augmented Reality Applications on Mobile Devices**

Ping-Han Chou, Shih-En Wei and Chun-Han Lin

- 12 **Energy-Efficient Frequency Selection Method for Bio-Signal Acquisition in AI/ML Wearables**

Hossein Taji, José Angel Miranda Calero, Miguel Peón Quiros and David Atienza Alonso

- 13 **VisionHD: Towards Efficient and Privacy-Preserved Hyperdimensional Computing for Image Data**

Fatemeh Asgarinejad, Justin Morris, Tajana Rosing and Baris Aksanli

- 14 **ComBoost: An Instruction Complexity Aware DTM Technique for Edge Devices**

Seung Hun Choi, Joonho Kong and Sung Woo Chung

- 15 **JointNF: Enhancing DNN Performance through Adaptive N:M Pruning across both Weight and Activation**

Sai Qian Zhang, Thierry Tambe, Gu-Yeon Wei and David Brooks

- 16 **HeTraX: Energy Efficient 3D Heterogeneous Manycore Architecture for Transformer Acceleration**

Pratyush Dhingra, Jana Doppa and Partha Pratim Pande

- 17 **Efficient Transformer Accelerator via Reconfiguration for Encoder and Decoder Dual Modes with Sparsity-Aware Data Mapping**

Chang Eun Song, Ashkan Moradifirouzabadi, Tajana Rosing and Mingu Kang

- 18 **Hardware-friendly Hessian-driven Row-wise Quantization and FPGA Acceleration for Transformer-based Models**

Woohong Byun, Jongseok Woo and Saibal Mukhopadhyay

- 19 **A 16nm Heterogeneous Accelerator for Energy-Efficient Sparse and Dense AI Computing**

Gopikrishnan Raveendran Nair, Fengyang Jiang, Jeff Zhang and Yu Cao

- 20 **Low Overhead Logic Locking for System-Level Security: A Design Space Modeling Approach**

Long Lam, Maksym Melnyk and Michael Zuzak

- 21 **OFHE: An Electro-Optical Accelerator for Discretized TFHE**

Mengxin Zheng, Cheng Chu, Qian Lou, Nathan Youngblood, Mo Li, Sajjad Moazeni and Lei Jiang

# ORGANIZING COMMITTEE

## **General Chair**

Pascal A. Meinerzhagen, Intel

## **Technical Program Co-Chairs**

Kapil Dev, Nvidia

Jerald Yoo, Seoul National University

## **Treasurer**

Mehdi Kamal, University of Southern California

## **Local Arrangements Chair**

Mehdi Kamal, University of Southern California

## **Web Co-Chairs**

Ganapati Bhat, Washington State University

Meron Zerihun Demissie, University of Michigan

## **Publications Chair**

Younghyun Kim, Purdue University

## **Design Contest Co-Chairs**

Rajesh Kedia, Indian Institute of Technology Hyderabad

Payam Heydari, University of California, Irvine

## **Publicity Co-Chairs**

Semeen Rehman, Technische Universität Wien

Jaeha Kung, Korea University

Linghao Song, University of California, Los Angeles

## **Registration Chair**

Ganapati Bhat, Washington State University

## **Industrial Liaison**

Adam Teman, Bar-Ilan University

Amlan Ganguly, Rochester Institute of Technology

# EXECUTIVE COMMITTEE

Massoud Pedram (EC Chair), University of Southern California

Luca Benini, University of Bologna

Naehyuck Chang, KAIST

Joerg Henkel, Karlsruhe Institute of Technology

Rajiv Joshi, IBM TJ Watson Research Center

Pai Chou, University of California, Irvine

Muhammad Khellah, Intel Corporation

Enrico Macii, Politecnico di Torino

Diana Marculescu, Carnegie Mellon University

Renu Mehra, Synopsys

Hiroshi Nakamura, The University of Tokyo

Wolfgang Nebel, Carl von Ossietzky Universität Oldenburg

Vijaykrishnan Narayanan, Pennsylvania State University

Vojin Oklobdzija, University of California, Davis

Massimo Poncino, Politecnico Di Torino

Jan M. Rabaey, University of California, Berkeley

Vijay Raghunathan, Purdue University

Kaushik Roy, Purdue University

Mircea Stan, University of Virginia

Vivek Tiwari, Intel Corporation

Yuan Xie, University of California, Santa Barbara

Chia-Lin Yang, Nanyang Technological University

# TECHNICAL PROGRAM COMMITTEE

## Track 1. Technology, Circuits, and Architecture

### 1.1-1.2. Technologies and Circuits

Rahul Rao (Track Co-Chair), IBM

Amit Agarwal (Track Co-Chair), Intel

Deliang Fan, Arizona State University

Fady Abouzeid, ST Microelectronics

Frank Gurkaynak, ETH Zurich

Joycee Mekie, IIT Gandhinagar

Inhee Lee, University of Pittsburgh

Samantak Gangopadhyay, Meta

Alexandre Levisse, EPFL

Karem Camsari, University of California, Santa Barbara

Srividhya Venkataraman, AMD

Ralf Brederlow, Technical University of Munich

### 1.3. Logic and Architecture

Rangharajan Venkatesan (Track Co-Chair), Nvidia

Kshitij Bhardwaj (Track Co-Chair), LLNL

Adam Teman, Bar-Ilan University

Daniel Wong, University of California, Riverside

Marisa Lopez-Vallejo, Universidad Politécnica de Madrid

Matthias Korb, ETH Zurich

Theocharis Theocharides, University of Cyprus

M. Hassan Najafi, University of Louisiana

Yang (Katie) Zhao, University of Minnesota

Marco Donato, Tufts University

Swagath Venkataramani, IBM

## Track 2. CAD, Systems, and Software

### 2.1. CAD Tools and Methodologies

Azadeh Davoodi (Track Co-Chair), University of Wisconsin-Madison

Enrico Macii (Track Co-Chair), Politecnico di Torino

Alberto Macii, Politecnico di Torino

Matthew Ziegler, IBM

Alessio Burrello, University of Bologna

Francesco Regazzoni, USI

Donkyu Baek, Chungbuk National University

Nadine Azemard-Crestani, LIRMM

Sanghamitra Roy, Utah State University

Caaliph Andriamisaina, CEA-Leti

Yuko Hara-Azumi, Tokyo Institute of Technology

Aida Todri-Sanial, TU Eindhoven

### 2.2. Systems and Platforms

Hun Seok Kim (Track Co-Chair), University of Michigan

Jason Xue (Track Co-Chair), City University of Hong Kong

Donghwa Shin, Soongsil University

Massimo Poncino, Politecnico di Torino

Pai Chou, National Cheng Kung University, Taiwan

Jaehyun Park, University of Ulsan

Mohammad Al Faruque, University of California, Irvine

Hussam Amrouch, Technical University of Munich

Taeyoung Kim, Intel

William Fornaciari, Politecnico di Milano

Ganapati Bhat, Washington State University

Santhosh Rethinagiri, Infineon

Naehyuck Chang, KAIST

Rajesh Kedia, IIT, Hyderabad

Anuj Pathania, University of Amsterdam

Hyung Gyu Lee, Duksung University

### 2.3. Software and Applications

Xue Lin (Track Co-Chair), Northeastern University

Daniele Jahier Pagliari (Track Co-Chair), Politecnico di Torino

Ittetsu Taniguchi, Osaka University

Aporva Amarnath, IBM

Yuan-Hao Chang, Academia Sinica

Young Geun Kim, Korea University

Jalil Boukhobza, ENSTA-Bretagne

Wanli Chang, University of York

Geng Yuan, University of Georgia

Victor Kartsch, ETH Zurich

Leonardo Piga, Meta

## Track 3. Crosscutting Topics

### 3.1. AI/ML Hardware, Compute-in-Memory (CIM) and Next-Generation Computing

Greg Chen (Track Co-Chair), Intel

Aatmesh Shrivastava (Track Co-Chair), Northeastern University

Divya Akella Kamakshi, Nvidia

Shaahin Angizi, New Jersey Institute of Technology

Kanad Basu, University of Texas Dallas

Edison Chen, Sambanova

Shanshi Huang, HKUST

Jan Moritz Joseph, RWTH

Georgios Karakontantis, Queen's University Belfast

Phil Knag, Intel

Gokul Krishnan, Apple

Kangmin Lee, Google

Youngjoo Lee, POSTECH

Sumit Mandal, Indian Institute of Science

Nikita Mirkhandidi, On Semi

Ivan Miro-Panades, CEA

Nitin Nitin, Nvidia

Srivatsa Rangachar Srinivasa, Intel

Arman Roohi, University of Nebraska

Abhronil Sengupta, Pennsylvania State University

Jae-sun Seo, Cornell University

Thierry Tambe Stanford, Nvidia

Amit Trivedi, University of Illinois

Xiaolin Xu, Northeastern University

### 3.2. Hardware and System Security

Anupam Chattopadhyay (Track Co-Chair), Nanyang Technological University

Debayan Das (Track Co-Chair), Indian Institute of Science

Kaveh Shamsi, University of Texas Dallas

Debjyoti Bhattacharjee, IMEC

Avinash Varna, Intel

Jeyavijayan Rajendran, Texas A&M University

Dirmanto Jap, Nanyang Technological University

Jakub Breier, TTControl

Chester Rebeiro, IIT Madras

Farhad Merchant, Newcastle University

Anupam Golder, Intel

Utsav Banerjee, Indian Institute of Science

Urbi Chatterjee, IIT Kanpur

Sayandee Saha, UC Louvain

Aydin Aysu, NCSU

Ujjwal Guin, Auburn University

Amitabh Das, AMD